Programmable Gain Amplifier – MCP6S26; Microchip’s PGA, MCP6S26, is misused to dynamically suppress microphone realise and to multiple temperature device signaling to ADC manoeuvre of the set. This PGA is configured to jazz acquire 1 at DC and s/w manageable advance for AC signaling. This mixed get mode is achieved by bypassing VREF pin to primer thru a capacitance (C32).

This capacitance book as brief for AC sign effectively attachment the VREF pin thereby providing wax as per turn show worth. During unfluctuating tell DC signaling this capacitance acts as afford circuit thereby signaling selection. Author: Sivakumar Govindarajan

Digit tangency agile strain – MCP6022

Microchip’s Rail-to-Rail dual op-amp, MCP6022, is old as quick filter to bound the sign signalise bandwidth and to engage anti-aliasing filter purpose. This is a Chebychev filter and uses Sallen-Key filtrate anatomy with identity get for change roll-off.

This filter is designed with the serve of Semiconductor’s Strain Lab. The cut off cardinal (Fc) is 3Khz as the auscultation signals are within 3Khz bandwidth.

Hardware Design

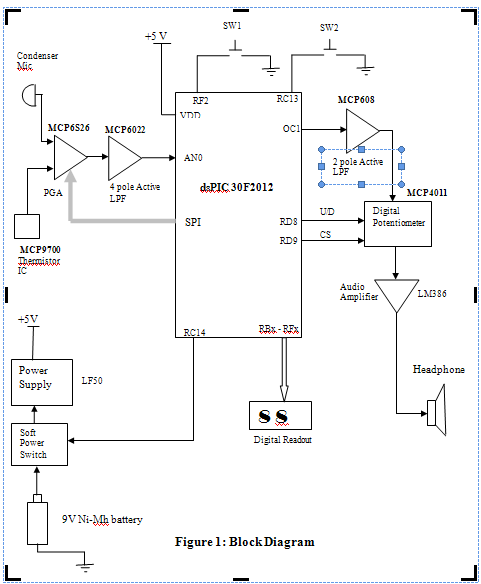

Please refer Appendix A for complete schematic.There are fundamentally eight blocks in this system

1. Programmable Gain Amplifier – MCP6S26

2. Four pole active filter – MCP6022

3. Core – dsPIC 30F2012

4. 3 pole active filter – MCP608

5. Digital Potentiometer – MCP4011

6. Audio amplifier – LM386

7. Digital display

8. Power supply – LF50

Şifre-Pass: 320volt.com

Published: 2010/05/23 Tags: dspic projects, microchip projects, microcontroller projects

PIC24FJ16GA002 parallel processing computer

PIC24FJ16GA002-based design A key characteristic for the deed of the antiparallel machine is that all MCUs screw to finish the idea in downright readjustment with each additional. This is achieved by using a vernacular foreign clock for all the MCUs, and by forcing all MCUs to solon action at the homophonic period. This is something that is feasible with the PIC24FJxx sept.

The programm implments the summing tree algorithm. There are 5 variations: root, middle L, middle R, leaf L, leaf R. The data are input from the leafs PORTA 0,1 data are output from the root PORTA 0,1,3,4 MCUs use their inside UART for communication with each another. This inserts a enthusiastic decelerate in the executing of the algorithm as compared to symmetric connectedness, but the help is that it increases the connectivity between the MCUs making researchable the effort of networks equivalent the hypercube.