Sayısal devreler hakkında mükemmel bir anlatım tüm detaylar uygulamaların bulunduğu görseller, şemalar ile desteklenmiş döküman. Hazırlayan: Yrd.Doç.Dr. Feza BUZLUCA Emeği geçen kişilere Teşekkürler çok güzel bir çalışma dosya .pdf formatında özellikle renkli olan görseller ile çok iyi daha kolay anlıyorsunuz.

Sayısal Develer Ders Notları 1

Analog – Sayısal (Dijital) İşaretler:

Sayısal Sistemlerin Avantajları:

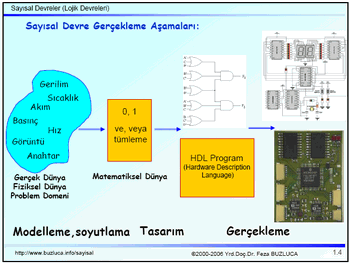

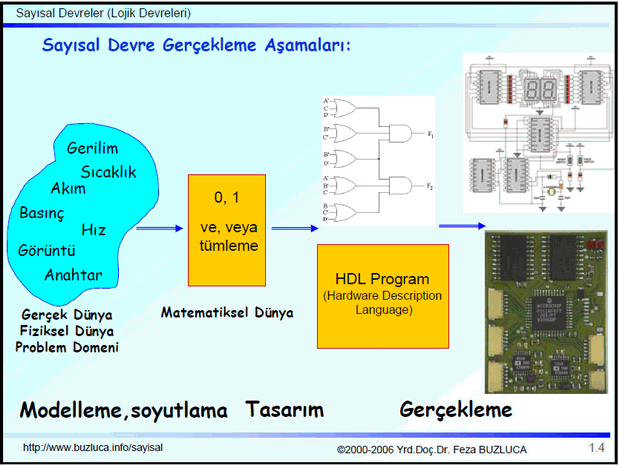

Sayısal Devre Gerçekleme Aşamaları:

Sayısal Kodlama:

BCD (Binary Coded Decimal) İkili kodlanmış onlu sayılar:

Ağırlıklı Kodlama:Hamming uzaklığı:Bitişik kodlar:

Sayıların Bilgisayarda Gösterilimi

Sayısal Sistemlerde Toplama ve Çıkarma İşlemleri

Elde (Carry), Borç (Borrow), Taşma (Overflow) Kavramlarının Özeti

Boole Cebri Sıra bağıntısı:Lojik Fonksiyonlar Lojik Fonksiyonların Gösterilişi

Grafik Gösterilim Karnaugh Diyagramları (Karnaugh Map) Cebirsel Gösterilim

Kanonik Açılım:,Kanonik Açılımların Dönüştürülmesi Kanonik Açılımlar ve De Morgan Teoremi

Sayısal Develer Ders Notları 2

Lojik Bağlaçlar (Logic Gates

Tümdevreler ( Integrated Circuits – IC ),Dual in-line Pin (DIP) Tümdevreler

Pozitif ve Negatif Lojik,Lojik Fonksiyonların Bağlaçlar İle Gerçeklenmesi

Doğruluk tablosu verilen fonksiyonun lojik bağlaçlar ile gerçeklenmesi

Yetkin İşlemler,TVE – TVEYA Arasındaki İlişki

Lojik fonksiyonların TVE veya TVEYA bağlaçları ile gerçeklenmesi

Toplamların çarpımı (VEYA’ların VE’si) şeklindeki fonksiyonların TVEYA ile gerçeklenmesi:

Sayısal Develer Ders Notları 3

Lojik Fonksiyonların Yalınlaştırılması (İndirgenmesi)

Yalınlaştırma: Uygun Asal Çarpımların Seçilmesi

Tümüyle Tanımlanmamış Fonksiyonların Yalınlaştırılması

Genel Fonksiyonların Yalınlaştırılması

Tüm Asal Çarpımlar Kümesinin Tablo Yöntemiyle (Quine-McCluskey) Bulunması

Sayısal Develer Ders Notları 4

Tümleştirilmiş Kombinezonsal Devre Elemanları

Veri seçicilerin kullanımına bir örnek:

Veri Seçiciler ile Genel Amaçlı Lojik Devre Tasarımı

Yayıcı Makas (Demultiplexer):

Kod Çözücüler ile Genel Amaçlı Lojik Devre Tasarımı:

Programlanabilir Lojik Elemanlar (Programmable Logic Device- PLD)

Programlanabilir Dizi Lojiği (Programmable Array Logic – PAL)

Programlanabilir Lojik Dizi (Programmable Logic Array – PLA)

İzin Girişli (EN) Kod Çözücü:

Sayısal Develer Ders Notları 5

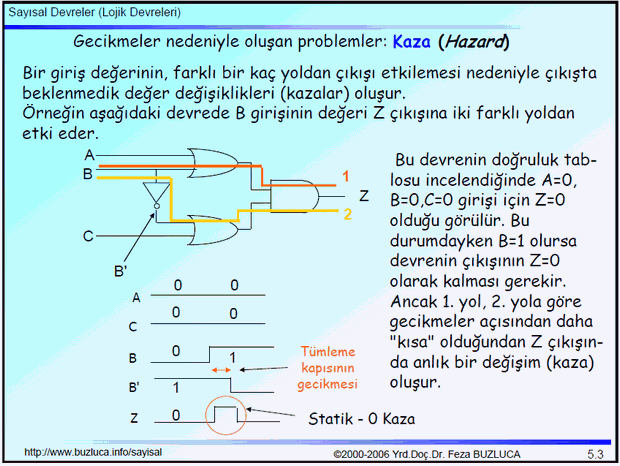

Zaman Diyagramları (Timing Diagrams)

Propagasyon Gecikmesi (Propagation Delay)

ARDIŞIL DEVRELER (Sequential Circuits)

Sonlu Durumlu Makine (Finite State Machine- FSM) Modeli

Veri Saklama (Bellek) Elemanları

Saat (Clock) İşareti:İki Kararlı (Bistable) Devre

S-R (Set-Reset) Bilgi Saklama Elemanı

İzin Girişli S-R Bilgi Saklama Elemanı

Tutucu (Latch), Flip-flop Farkı:İzin Girişli S-R Tutucu

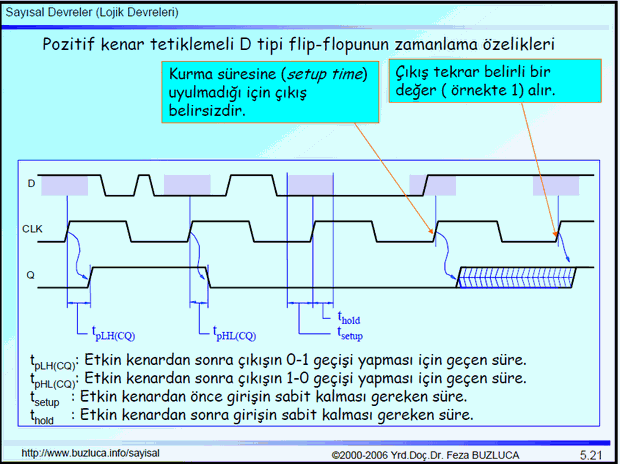

D tipi Tutucu (Delay Latch)Pozitif (çıkan) kenar tetiklemeli D tipi Flip-flop

Negatif (inen) kenar tetiklemeli D tipi Flip-flopu

Kenar tetiklemeli ve izin girişli D tipi Flip-flopu

Ana/Uydu (Master/Slave) tipi SR Flip-flopu,JK Tutucu

Kenar Tetiklemeli JK Flip-flopu Kenar tetiklemeli T Flip-Flopu (Toggle Flip-flop)

Sayısal Develer Ders Notları 6

Senkron Ardışıl Devreler (Synchronous Sequential Circuits)

Senkron ardışıl devrelerin çözümlenmesi (Analiz)

JK Flip-flopları ile tasarlanmış bir senkron ardışıl devrelerin çözümlenmesi

Moore modeline göre tasarlanmış bir ardışıl devrenin çözümlenmesi:

Mealy ve Moore Modellerinde Çıkışların Yorumlanması

Sayısal Develer Ders Notları 7

Senkron Ardışıl Devrelerin Tasarlanması (Design)

Senkron Devrelerin Gerçeklenmesinde Veri Seçicilerin Kullanılması

Sayısal Develer Ders Notları 8

sayısal elemanların İç yapıları

Bir Tümleme kapısının tranzistor ve dirençle gerçeklenmesi

TTL (Tranzistor- Tranzistor) Lojiği Ailesi

TTL Çıkış Katının Çalışması

TTL Çıkış Yelpazesi (Fan Out)

CMOS (Complementary MOS) Lojiği Ailesi

CMOS Tümleme Bağlacı

CMOS Tümleme Bağlacının Anahtar Modeli

CMOS TVE (NAND) Bağlacı

CMOS TVE (NAND) Bağlacı Anahtar Modeli

CMOS TVEYA (NOR) Bağlacı

Dosyaları Buradan indirebilirsiniz

Şifre-Pass: 320volt.com

Yayım tarihi: 2008/02/16 Etiketler: boole cebri, dijital elektronik, lojik devre tasarımı, lojik devreler, lojik kapı devreleri, lojik kapılar, lojik uygulamalar, nand kapısı, not kapısı, or kapısı, sayısal devreler

lojik kapıya buton bağlama hakkında bilgi verir misiniz acaba resim olursa sevinirim.saygılar

lojik devrelerle ilgili konu araştırıyorum ama bulamadım açil lazım resi veya anlatım olursa sevinirim

kabloları direkt butana bağla enerla sonrada lojik devreye ver bu kadar basit

iyi günler. bir konuda yardıma ihtiyacım var.4 bitlik veriyi 2 adet 4511 ile 2 adet display sürmek istiyorum.4 bitlik gelen veri 10 dan küçükse benim seçtiğim ilk displayde cıkan sayıyı görmek istiyorum.Ama 10 dan büyükse mesela “13” ü

“1” ve “3” diye görmek istiyorum.Bu konuda yardımcı olursanız sevinirim.

bilgisayar bölümü öğrencisiyim yıllık ödev olarak temel elektrnk dersinden ödev aldım…konu lojik devre tasarımı araştırılacak 5 tne de soru yazılcak ama hiç bir bilgim yok bu konuda araştırdm fakat bulamadm…yardım edersenz sevinirim…

Aynen benimde proje ödevim dijital devre elemanlarının tanımı bir bilginiz varsa lütfen paylaşın