Giriş : Bu tezde anlatılan projenin gerçeklenmesindeki amaç, bilgisayarın PCI slotuna yerleştirilecek FPGA tabanlı bir PCI kartı tasarlayarak bilgisayar ile dış dünyadaki sistemler arasında yüksek hızlı seri veri alış verişi yapmaktır.

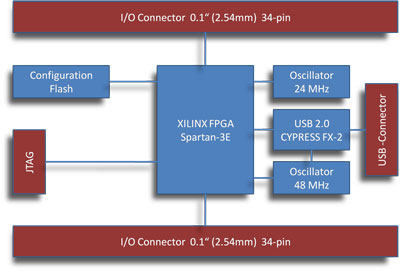

Projenin gerçeklenebilmesi için birçok aşamadan geçilmesi gerekmektedir. Öncelikle yapılması gereken PCI veri yolu mimarisinin çalışmasını kavramaktır. Daha sonra ise isteklerimizi karşılayabilecek bir FPGA seçimi ve bu FPGA’in özelliklerinin iyice kavranması ardından PCI iletişimi için kullanılacak IP Core’un belirlenmesi, seri veri iletim arayüzünün seçilmesi ve devre tasarımı için kullanılacak programın belirlenmesiyle şematik tasarımı gerçekleştirilerek PCB tasarımının yapılması ve son aşamada kartın montajının yapılması gerekmektedir.

Kartın montajı tamamlandığında sıra yazılım kısmına gelecektir. Öncelikle FPGA’e yüklenecek program hazırlanıp EPROM’a aktarılmalı ve kartın testlerinin yapılması gerekmektedir. Testler olumlu sonuçlandığında en son aşama olarak kartın aygıt sürücüsü ve programının yazılması ve ardından sistemin çalışır hale getirilmesi ile tasarım sonuçlandırılacaktır.

Bu tezde önce PCI veri yolu mimarisi genel hatlarıyla anlatılmaya çalışılmış, ardından devre tasarımında kullanılacak FPGA ve SERDES elemanları incelenmiş, VHDL ve LVDS standardı tanıtılmış ve devre tasarımının EAGLE programı kullanılarak nasıl yapıldığı anlatılmıştır.

PCI V2.2 Yerel veri yolu mimarisi : PCI veri yolu mimarisi adres ve veri yollarının birlikte kullanıldığı yüksek performanslı 32 yâda 64 bitlik bir veri yoludur. Bu veri yolu, tümleşik çevre birimi kontrol cihazları ile çevre birimi add-in kartları ve işlemci/hafıza sistemleri arasında bir bağlantı mekanizması olarak kullanmak için tasarlanmıştır.

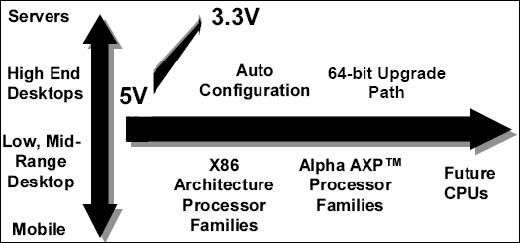

PCI Veri yolu Uygulamaları :PCI veriyolu, birinci amaç olarak bir endüstri standardı oluşturarak düşük maliyetli yüksek performans sunan veri yolu mimarisi olarak sunulmuştur. Günümüz sistemlerine yeni fiyat-performans noktaları sunarken, gelecekteki sistem ihtiyaçlarını karşılamak ve çoklu platformlar ve mimarilere de uygulanabilirlik de çok önemlidir.

Şekil 2.1 PCI Yerel Veriyolu Uygulamaları

Yerel veriyolu uygulamalarının ilk odağı alt ve üst uç masaüstü sistemleri iken, PCI yerel veri yolu aynı zamanda mobil uygulamalarından büyük sunuculara kadar olan ihtiyaçları da karşılamaktadır (Şekil 2.1). PCI elemanları ve add-in kart arayüzü işlemciden bağımsızdır ve bu gelecek nesil işlemcilere verimli geçişe ve çoklu işlemci mimarileri ile birlikte kullanıma izin verir.

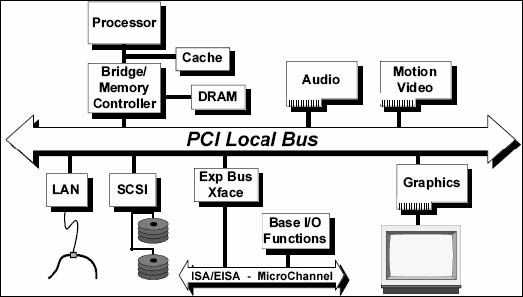

işlemciden bağımsızlık PCI veri yoluna G/Ç işlevleri için optimizasyon sağlar, işlemci/hafıza altsistemi ile yerel veriyolunun uyumlu çalışmasına olanak sağlar ve grafiklere ek olarak çoklu yüksek performanslı çevrebirimlerini barındırır (hareketli video, LAN, SCSI, FDDI, sabit disk sürücüleri v.s.). Gelişmiş video ve çoklu ortam displayler (HDTV ve 3B grafikler) ve diğer yüksek bantgenişlikli G/Ç’lar veri yolu bantgenişliği ihtiyacını arttırmaya devam etmektedir. PCI BUS V2.2, ileriye ve geriye uyumlu 32 bit ve 64 bit veri yoluna sahip 33MHz ve 66MHz veriyolu mimarisi desteği sağlamaktadır. Şekil 2.2’de PCI sisteminin blok yapısı görülmektedir.

Sekil 2.2 PCI Sistemi Blok Diyagramı

PCI Veriyolu Özellikleri ve Avantajları : PCI veriyolu çeşitli ürün kuşaklarına yüksek performanslı bir yerel veriyolu standardı oluşturmak için tanımlanmıştır. PCI özellikleri aşağıdaki avantajlarla kategorize edilmiştir.

Yüksek performans:

• 33MHz 32bit (132MB/s) veriyolundan 33MHz 64bit (264MB/s) veriyoluna ve 66MHz 32bit (264MB/s) veriyolundan 66MHz 64bit (528MB/s) veriyoluna kolay güncelleme.

• Değişken uzunluklu lineer ve yazma ve okuma için cacheline wrap mode bursting, yazmaya bağımlı grafik performansını arttırır.

• işlemci/hafıza altsistemi ile tamamen uyum kabiliyeti.

• 33MHz yâda 66MHz’e kadar senkronize veriyolu.

• Gizli merkezi sorun çözme.

Düşük maliyet:

• Doğrudan silikon bağlantısı için optimize edilmiştir. Elektriksel/sürücü ve frekans şartnameleri standart ASIC teknolojisi ve diğer proseslerle uyumlu.

• Çoklayıcılı mimari PCI elemanlarının boyutunu ve pin sayısını azaltmaktadır.

Kullanım kolaylığı:

• PCI add-in kartları ve bileşenlerinin tam otomatik yapılandırma desteğine izin verir. PCI aygıtları, yapılandırma için gereken aygıt bilgilerini barındıran saklayıcıları barındırmaktadır.

Uzun ömür:

• işlemciden bağımsızdır. Gelecek nesil işlemciler gibi çoklu işlemci ailelerini destekler (köprü yâda doğrudan bütünleşerek).

• 64bit adreslemeyi destekler.

• 5V ve 3.3V işaretleşme ortamları belirtilmiştir.

Güvenilirlik:

• Küçük boyutlu add-in kartlar

• Present sinyalleri, güç kaynaklarının add-in kartları gözlemleyerek beklenen sistem kullanımı için optimize edilmesine olanak sağlar.

• 32bit ve 64bit add-in kartları ve bileşenlerinin ileriye ve geriye uyumluluğu.

• 33MHz ve 64MHz add-in kartları ve bileşenlerinin ileriye ve geriye uyumluluğu.

• MC-türü genişleme konektörleri.

Esneklik:

• Her hangi PCI master/target’dan her hangi bir PCI master’a noktadan noktaya erişime izin veren tam multi-master kabiliyeti.

• Paylaşımlı bir slot, standart ISA, EISA veya MC kart yâda bir PCI add-in karta yer sağlar.

Veri doğruluğu:

• Robust client platformlarının gerçeklenmesine olanak sağlayan veri ve adres üzerinde eşlik sağlar.

Yazılım uyumluluğu:

• PCI bileşenleri, mevcut sürücü ve uygulama yazılımları ile tam uyumlu olabilmektedir. Aygıt sürücüleri çeşitli platform sınıfları için taşınabilirdir.

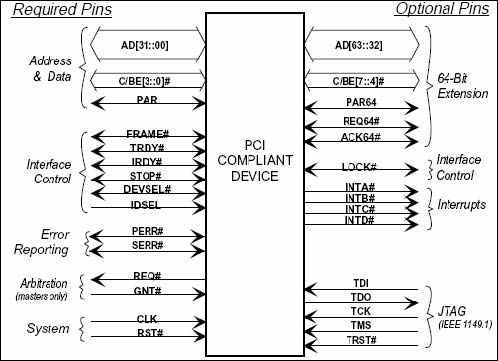

Sinyal Tanımı : PCI arayüzü target-only bir aygıt için minimum 47, veri ve adresleme, arayüz kontrol, sorun çözme (arbitration) ve sistem fonksiyonlarını idare eden bir master için en az 49 pin gerektirmektedir. Şekil 2.3’de PCI pinleri solda gerekli pinler ve sağda opsiyonel pinler olmak üzere fonksiyonel gruplar halinde gösterilmektedir. Sinyallerin sonundaki # simgesi, sinyalin aktif sıfır olduğunu göstermektedir.

Sistem Pinleri :

CLK: Saat (Clock), PCI üzerindeki tüm işlemler için zamanlamayı sağlamaktadır ve bütün PCI cihazları için giriştir. Diğer tüm PCI sinyalleri (RST#, INTA#, INTB#,INTC# ve INTD# dışında) CLK’nın yükselen kenarında örneklenir ve tüm diğer zamanlama parametreleri bu kenara uyarak tanımlanır. PCI 33MHz yâda 66MHz’e kadar çalışır ve genellikle minimum frekans DC (0Hz)’dir.

RST#: Reset, PCI-özgül saklayıcıları, sıralayıcı ve sinyalleri, uygun bir duruma getirmekte kullanılmaktadır. RST # sinyali verildiğinde tüm PCI çıkış sinyalleri başlangıç durumlarına sürülmelidir. Genellikle bu çıkışların asenkron olarak tri-state konumuna geçmesi demektir. REQ# ve GNT# de tri-state konumunda olmalıdır. AD, C/BE# ve PAR sinyallerinin reset durumunda boşta kalmalarından kaçınmak için merkezi kaynak reset sırasında bu hatları (lojik 0 olarak) sürebilir (bus parking). RST#, CLK ile asenkron olabilir.

Sekil 2.3 PCI Pin Listesi

Adres ve Veri Pinleri

AD[31::00]: Adres ve Veri aynı PCI pinleri üzerinde çoklanmışlardır. Bir bus işlemi bir adres fazı ve ardından bir yâda daha fazla olan veri fazından meydana gelir. Adres fazı FRAME# sinyali aktif edildiğindeki ilk saat çevrimidir. Adres fazında, AD[31::00] fiziksel adresi (32bit) içerir. Bu G/Ç için bir byte adresi, yapılandırma ve hafıza için ise bir DWORD adresidir. Veri fazında AD[07::00] en az anlamlı byte’ı (lsb), AD[31::24] ise en anlamlı byte’ı (msb) içermektedir. IRDY# aktifken yazılan veri sabit ve geçerli, TRDY# aktifken okunan veri sabit ve geçerlidir. Veri IRDY# ve TRDY#’nın her ikisi aktifken bu saat çevrimleri süresince transfer edilir.

C/BE[3::0]#: Bus Komutu (Bus Command) ve Byte Yetkilendirme (Byte Enable) aynı PCI pinlerinde çoklanmışlardır. Bir işlemin adres fazı süresince C/BE[3::0]# Bus komutlarını tanımlamaktadır. Veri fazı süresince ise Byte yetkilendirme olarak kullanılır. Byte yetkilendirme bütün veri fazı için geçerlidir ve hangi byte yolunun anlamlı veri taşıdığını belirtir. C/BE[0]# byte 0 (lsb)’ı, C/BE[3]# byte 3 (msb)’ü temsil etmektedir.

PAR: Eşlik (parity), AD[31::0] ve C/BE[3::0]# için çift eşliktir. Eşlik üretme tüm PCI vasıtaları tarafından istenmektedir. PAR her bir adres fazından sonraki bir çevrim boyunca sabit ve geçerlidir. Veri fazları için, yazma işlemlerinde IRDY# veya okuma işlemlerinde TRDY#’den herhangi birinin aktif edilmesinden sonraki bir çevrim boyunca sabit ve geçerlidir. PAR bir kez geçerli olduğunda geçerli veri fazının tamamlanmasından sonraki bir çevrime kadar geçerli kalır. PAR AD[31::00] ile aynı zamanlamaya sahiptir fakat bir çevrim geciktirilmiştir. Master, adres ve veri yazma fazları için PAR’ı sürerken Target, veri okuma fazlarında PAR’ı sürmektedir.

Arayüz Kontrol Pinleri

FRAME#: Çerçeve çevrimi (Frame Cycle), bir erişim başlangıcını ve süresini belirtmek için geçerli master tarafından sürülmektedir. FRAME# bir bus işleminin başladığını belirtmek için aktif edilir. FRAME# aktif olduğu sürece veri transferi devam eder. FRAME# kaldırıldığında işlem son veri fazında yâda tamamlanmıştır.

IRDY#: Başlatıcı Hazır (Initiator Ready), mevcut veri fazı işleminin tamamlanması için başlatıcı aracının (Bus Master’ın) hâkimiyetini gösterir. IRDY#, TRDY# ile birlikte kullanılır. Veri fazı IRDY# ve TRDY# nin ikisi de aktif edildiği herhangi bir çevrimde tamamlanır. Yazma süresince IRDY# AD[31::00] üzerinde geçerli bir verinin olduğunu belirtir. Okuma süresince, Master’ın veriyi kabul etmeye hazırlandığını belirtir. Bekleme çevrimleri IRDY# ve TRDY# birlikte aktif olana kadar eklenir.

TRDY#: Target Hazır (Target Ready), mevcut veri fazı işleminin tamamlanması için target aracının (seçilen sürücünün) hâkimiyetini gösterir. TRDY#, IRDY# ile birlikte kullanılır. Veri fazı, TRDY# ve IRDY# nin ikisi de aktif edildiği herhangi bir çevrimde tamamlanır. Okuma süresince TRDY# AD[31::00] üzerinde geçerli bir verinin olduğunu belirtir. Yazma süresince, Target’ın veriyi kabul etmeye hazırlandığını belirtir. Bekleme çevrimleri TRDY# ve IRDY# birlikte aktif olana kadar eklenir.

STOP#: Stop, geçerli Target’in, Master’a mevcut işlemi durdurması için istekte bulunduğunu gösterir.

LOCK#: Lock, tamamlanması için çoklu işlemler gerektirebilen bir Bridge’e yapılan atomik işlemleri göstermektedir. LOCK# aktif edildiğinde özel olmayan işlemler o anda kilitli olmayan bir Bridge’de yürütülebilir. Kilitli işlemler sadece Host Bridge, PCI-to-PCI bridge ve expansion bus bridge tarafından başlatılabilir.

IDSEL: Sürücü başlatma seçme (Initialization Device Select), yapılandırma okuma ve yazma işlemleri süresince bir çip seçme (chip select) olarak kullanılır.

DEVSEL#: Sürücü Seçme (Device Select), aktif olarak sürüldüğünde, sürülen aygıtın kendi adresini geçerli erişimin köprüsü olarak çözdüğünü belirtir. Giriş olarak DEVSEL#, bus üzerindeki herhangi bir aygıtın seçilip seçilmediğini belirtir.

Sorun Çözme (Arbitration) Pinleri

REQ#: jstek (Request), bir aracının (agent) veri yolunu kullanmak istediğini hakeme bildirmektedir. Bu, noktadan noktaya bir sinyaldir. Her bir Master, RST# aktif edildiğinde tri-state konumunda olması gereken, kendi REQ# sinyaline sahiptir.

GNT#: Onaylama (Grant), aracıya veri yoluna erişimin onaylandığını belirtmektedir.

Hata Raporlama Pinleri

PERR#: Eşlik Hatası (Parity Error), özel çevrim (Special cycle) dışındaki tüm PCI işlemleri süresince veri eşlik hatalarını raporlamak içindir. PERR# pini tri-state konumunda tutulmalı ve bir veri eşlik hatası olduğunda veriyi takip eden iki çevrimde aracı tarafından aktif edilmelidir. PERR# ‘in minimum süresi veri eşlik hatası tespit edilen her bir veri fazı için bir çevrimdir.

SERR#: Sistem Hatası (System Error), özel çevrim komutunda bir adres yâda veri eşlik hatası olduğunda yâda kötü bir sonuca neden olabilecek diğer sistem hatalarının rapor edilmesi içindir. Eğer bir aracı bir NMI kesmesinin oluşturulmasını istemiyorsa farklı bir raporlama mekanizmasına ihtiyaç duyulur. SERR#, saf open-drain’dir ve hatayı rapor eden aracı tarafından tek bir PCI çevrimi için aktif olarak sürülür.

Kesme Pinleri

PCI üzerindeki kesmeler seçime bağlıdır ve seviye hassasiyetli olarak tanımlanmıştır. INTx# aktif etme ve kaldırma CLK ile asenkrondur. Bir aygıt, mesaj işaretli kesmeleri (message signaled interrupts-MSI) kullanmaya yetkili ise, kendi aygıt sürücüsünden bir istekte bulunmak için INTx# sinyalini aktif eder. INTx# sinyali aktif edildiğinde, aygıt sürücüsü askıdaki isteği silene kadar aktif olarak kalır. istek silindiğinde, aygıt RSTx# sinyalini kaldırır. PCI tek fonksiyonlu aygıtlar için bir tane kesme hattı tanımlamaktadır. Tek fonksiyonlu aygıtlar için sadece INTA# kullanılabilirken diğer üç kesme hattının bir anlamı yoktur.

PCI’da INTA#, INTB#, INTC# ve INTD# olmak üzere dört adet kesme tanımlanmıştır.. Çok fonksiyonlu aygıttaki herhangi bir fonksiyon INTx# hatlarından herhangi birine bağlanabilmektedir. Kesme Pin saklayıcısı hangi INTx# hattının, hangi kesme isteği için kullanılacağını belirtmektedir.

Ek Sinyaller

PRSNT[1:2]#: Mevcut (Present) sinyalleri, aygıt sinyalleri değildir, fakat bir add-in kartı tarafından sağlanmaktadır. Present sinyalleri slotta fiziksel olarak bir add-in kartının bulunduğunu ve kartın toplam güç ihtiyacını belirtmektedir. Bu sinyaller add-in kartları için gereklidir ancak anakartlar için seçime bağlıdır.

CLKRUN#: Saat çalışıyor (Clock running), bir aygıta CLK’nın durumunu belirtmek için giriş olarak kullanılan seçime bağlı bir sinyaldir ve open-drain bir çıkış aygıt tarafından CLK’yı başlatma yâda hızlandırma isteği için kullanılmaktadır. CLKRUN#, merkezi kaynak (central resource) tarafından CLK’yı yavaşlatma yâda durdurma izni istemek için kullanılan bir sustained tri-state (s/t/s) sinyaldir. Merkezi kaynak CLK çalışıyorken CLKRUN#’ın aktif olarak kalmasından ve CLK’yı yavaşlatma yâda durdurma izni isteği için CLKRUN#’ı kaldırmaktan sorumludur.

M66EN: 66MHz_Enable pini, aygıta veri yolunun 66MHz yâda 33MHz’de çalıştığını bildirmektedir.

PME#: Güç Yönetimi olayı (Power Menagement Event) sinyali, aygıt tarafından aygıtta yâda sistem durumunda bir değişiklik isteği için kullanılan seçime bağlı bir sinyaldir. PME#’nin aktif edilmesi ve kaldırılması CLK ile asenkrondur.

3.3Vaux: Seçime bağlı 3.3 volt yardımcı güç kaynağı, bir PCI add-in kartın ana gücü yazılım tarafından kapatıldığında, güç yönetimi olayları üretmek için PCI add-in karta güç verir. PCI veri yolu güç yönetimini desteklemeyen bir sistem yâda add-in kartı, 3.3Vaux pinini ayrılmış (reserved) olarak ele almalıdır.

64-Bit Veri Yolu Genişleme Pinleri (Seçime Bağlı)

64-Bit genişleme pinleri toplu olarak seçime bağlıdır. Eğer 64-Bit genişleme kullanılacak ise bu bölümdeki bütün pinlerin kullanılması gerekmektedir.

AD[63::32]: Adres ve Veri aynı PCI pinleri üzerinde çoklanmışlardır ve 32 adet ek biti sağlamaktadır. Adres fazında (DAC komutu kullanırken ve REQ64# aktifken), 64-Bitlik adresin üst 32-biti transfer edilmektedir. Diğer durumlarda bu pinler ayrılmıştır fakat sabit ve belirsizdir. Veri fazında REQ64# ve ACK64# aktif edilerek 64-bit işlemi akdedildiğinde ek 32-bitlik veri transfer edilmektedir.

C/BE[7::4]#: Bus Komutu (Bus Command) ve Byte Yetkilendirme (Byte Enable) aynı PCI pinlerinde çoklanmışlardır. Adres fazı süresince (DAC komutu kullanırken ve REQ64# aktifken), asıl veri yolu komutu C/BE[7::4]# üzerinden transfer edilir. Veri fazı süresince ise Byte yetkilendirme olarak kullanılır. Byte yetkilendirme REQ64# ve ACK64# aktif edilerek 64-bit işlemi akdedildiğinde hangi byte yolunun anlamlı veri taşıdığını belirtir. C/BE[4]# byte 4 ’ü, C/BE[7]# byte 7 ’yi temsil etmektedir.

REQ64#: 64-Bit transfer isteği (Request 64-Bit Transfer), geçerli Bus Master tarafından aktif edildiğinde verinin 64-bit olarak transfer edilmek istendiğini belirtir. REQ64# aynı zamanda FRAME# ile aynı zamanlamaya sahiptir.

ACK64#: 64-bit transfer kabul (Acknowledge 64-bit Transfer), adresini gerçekten geçerli erişimin hedefi olarak çözen aygıt tarafından aktif olarak sürüldüğünde target’ın 64-bitlik veri transferine hazır olduğunu belirtmektedir.

PAR64: Eşlik yüksek DWORD (Parity Upper DWORD), AD[63::32] ve C/BE[7::4]’ü koruyan çift eşlik bitidir. PAR64, REQ64# aktifken her hangi bir işlemde her bir veri fazından sonraki bir çevrim geçerli kalmalıdır. 64-bit veri fazları süresince, yazma işlemlerinde IRDY# veya okuma işlemlerinde TRDY#’den herhangi birinin aktif edilmesinden sonraki bir çevrim boyunca sabit ve geçerlidir. PAR64 AD[63::32] ile aynı zamanlamaya sahiptir fakat bir çevrim geciktirilmiştir. Master, adres ve veri yazma fazları için PAR64’ü sürerken Target, veri okuma fazlarında PAR64’ü sürmektedir.

JTAG/Boundary Scan Pinleri (Seçime Bağlı)

IEEE 1149.1 standardı, Test Access Port ve Boundary Scan Mimarisi PCI aygıtları için seçime bağlı olarak dâhil edilmiştir. IEEE 1149.1 standardı, 1149.1-uyumlu çiplerin dizaynı için kulları ve izinleri belirtmektedir. Bir aygıta Test Erişim Portu (TAP) eklemek, aygıtı ve takılan kartı test etmede kullanılan boundary scan işlemine olanak sağlar. TAP, PCI aygıtı içerisinde TAP denetleyicisi ile seri olarak bağlamakta kullanılan dört pinden oluşmaktadır (opsiyonel olarak beş).

TCK (in): Test Clock, TAP işlemi süresince durum bilgisini ve aygıta giren ve çıkan test verilerini ölçmek için kullanılmaktadır.

TDI (in): Test Verisi Girişi (Test Data Input), TAP işlemi süresince seri olarak test verilerini ve test komutlarını aygıtın içine kaydırmakta kullanılmaktadır.

TDO (out): Test Çıkışı (Test Data Output), TAP işlemi süresince seri olarak test verilerini ve test komutlarını aygıtın dışına kaydırmakta kullanılmaktadır.

TMS (in): Test Modu Seçimi (Test Mode Select), aygıt içerisindeki TAP denetleyicisinin durumunu kontrol etmede kullanılmaktadır.

TRST#: Test Reset, TAP denetleyicisinin asenkron başlatılmasını sağlamaktadır. Bu sinyal, IEEE 1149.1’de seçime bağlı bir sinyaldir. Sistem satıcıları sistem içerisinde gereken 1149.1 seri zinciri (halka – “Ring”) işlemi ve dizaynından sorumludur. Tipik olarak bir 1149.1 halkası, aygıtların seri zincirini oluşturmak için bir aygıtın TDO pininin diğer aygıtın TDI pinine bağlanması ile oluşturulur. Bu uygulamada aygıtlar aynı TCK, TMS ve TRST# (opsiyonel) sinyallerini alırlar. IEEE 1149.1 standardını desteklemeyen genişlemek artları TDI ve TDO pinlerini donanımsal olarak kabloyla birbirine bağlamalıdır.

Elektrik Şartnamesi

5V’dan 3.3V’a Geçiş Yol Haritası

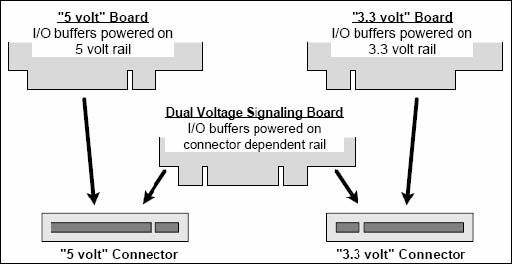

PCI elektrik şartnamesinin bir amacı 5V’dan 3.3V’luk bileşen teknolojisine kolay ve hızlı bir geçiş sağlamaktır. Bu geçişi kolaylaştırmak için PCI biri 5V diğeri 3.3V sinyalleşme ortamı için iki adet genişleme kartı konektörü tanımlamıştır. Konektörlerde bulunan çentikler sayesinde kartların yanlış konektöre takılması önlenmiştir. Buna karşın bu iki sinyalleşme ortamını destekleyen genel (Üniversal board) kartlar geliştirilmiştir. Bu kartlar sinyalleşme ortamını algılayabilme kabiliyetine sahiptirler. Bu sayede her iki konektöre de takılabilmektedirler. Şekil 2.4’de üç çeşit genişleme kartı ve sinyalleşme ortamı konektörleri görülmektedir.

Şekil 2.4 PCI Kart Konektörleri

5V Sinyalleşme Ortamı

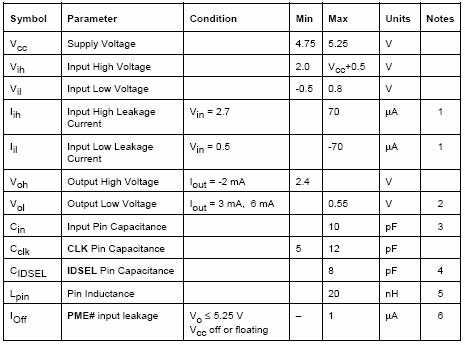

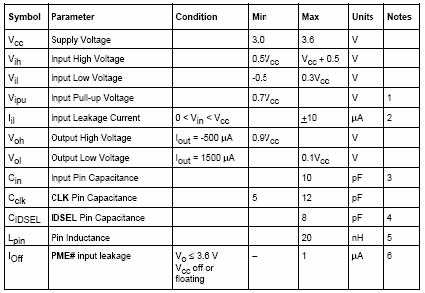

DC Şartnameler : Aşağıda tablo 2.1’de 5V sinyalleşme için DC şartnameleri özetlemektedir.

Tablo 2.1 5V DC Şartname

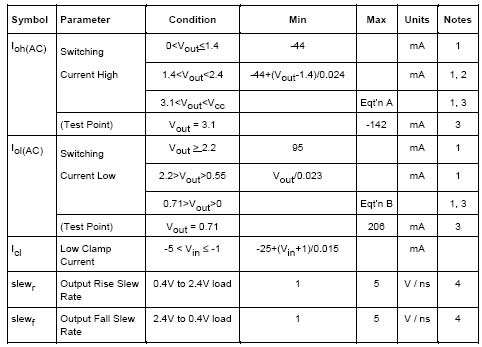

AC Şartnameleri : Aşağıda tablo 2.2’de 5V sinyalleşme için AC şartnameleri özetlemektedir.

Tablo 2.2 5V AC Şartname

3.3V Sinyalleşme Ortamı

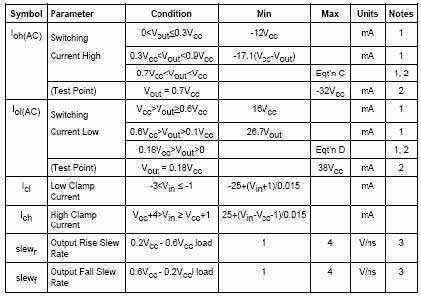

DC Şartnameleri : Aşağıda tablo 2.3’de 3.3V sinyalleşme için DC şartnameleri özetlemektedir.

Tablo 2.3 3.3V DC Şartname

AC Şartnameleri : Aşağıda tablo 2.4’de 3.3V sinyalleşme için AC şartnameleri özetlemektedir.

Tablo 2.4 3.3V AC Şartname

Dekuplajlama : Tipik koşullar altında Vcc düzeyinden toprak düzeyine olan kapasitans Vcc konektör pinleri için yeterli dekuplajlama sağlamaktadır. Bağlantı noktasından Vcc/toprak düzlemine olan maksimum yol uzunluğu 0.25 inç (yol genişliğini 20 mil varsayarsak) olmalıdır. Bununla beraber, üniversal kartlarda G/Ç tampon güç rayı gerekli dekuplajlamayı sağlamak için toprak düzlemine uygun kapasitansa sahip olması olasıdır. +VI/O olarak etiketlenmiş pinler, pin başına ortalama 0.0047uF’lık kapasite ile toprağa dekuple edilmelidir.

Spartan-3E FPGA Ailesi

Spartan-3E Alan Programlamalı Kapı Dizisi ailesi 5 üyeden oluşmaktadır (Bkz. Tablo 3.1). Bu beş üye toplam 100,000 ‘den 1.6 milyon’a kadar sistem kapı yoğunluğuna sahiptir. Spartan-3E ailesi I/O başına lojik kapı miktarının arttırılması ve lojik hücre başına olan maliyetin önemli ölçüde düşürülmesi ile daha önceki Spartan–3 ailesinin başarısı üzerine geliştirilmiştir. Yeni özellikler sistem performansını arttırmakta ve yapılandırma maliyetini azaltmaktadır. Spartan-3E’deki bu gelişimler 90nm işlem teknolojisi ile birleştirilerek daha fazla işlevsellik ve bant-genişliği getirmekte ve programlanabilir lojik endüstrisinde yeni standartlar sunmaktadır.

Fevkalade düşük maliyeti yüzünden Spartan-3E ailesi geniş-bant erişim, ev ağı, display/projeksiyon ve sayısal televizyon donanımları dâhil geniş bir tüketici elektroniği uygulamalarına uygundur.

Özellikleri:

• Yüksek seviyeli tüketici-yönelimli uygulamalar için çok düşük maliyetli yüksek performanslı lojik çözümü

• Kanıtlanmış gelişmiş 90nm işlem teknolojisi

• Çoklu-Gerilim, Çoklu-Standart SelectIO™ arayüz pinleri

• 376’ya kadar I/O pini yâda 156 fark sinyali çifti

• LVCMOS, LVTTL, HSTL ve SSTL single-ended sinyal standartları

• 3.3V, 2.5V, 1.8V, 1.5V ve 1.2V işaretleşme

• I/O başına 622+ Mb/s veri transfer oranı

• True LVDS, RSDS, mini-LVDS, differential HSTL/SSTL differential I/O

• Gelişmiş DDR (double data rate) desteği

• 333 Mb/s’a kadar DDR SDRAM desteği

• Bol ve esnek lojik kaynaklar

• Opsiyonel kaymalı kaydedici yâda dağıtılmış RAM desteği dâhil 33,192’e kadar lojik hücre yoğunluğu

• Verimli geniş çarpıcılar, geniş lojik

• Opsiyonel işhatlı gelişmiş 18×18 çarpıcılar

• Hiyerarşik SelectRAM™ bellek mimarisi

• 648Kbit’e kadar hızlı blok RAM

• 231 Kbit’e kadar verimli dağıtılmış RAM

• 8 adede kadar Sayısal Saat Yöneticisi (DCM)

• Saat eğim eleme (gecikme kilitli çevrim DLL)

• Frekans sentezi, çarpma, bölme

• Yüksek çözünürlüklü faz kaydırıcı

• Geniş frekans aralığı (5 MHz’den 300 MHz’in üzerine kadar)

• Sekiz global saat ile aygıtın her yarım bölümü başına sekiz ek saat artı bol düşük-eğimli yönlendirme

• Endüstri-standardı PROM’lar için yapılandırma arayüzü

• Düşük-maliyetli, yerden tasarruf sağlayan SPI seri Flash PROM

• X8 yâda x8/x16 paralel NOR Flash PROM

• Düşük maliyetli JTAG destekli Xilinx Platform Flash

• MicroBlaze ve PicoBlaze gömülü işlemce çekirdekleri

• Tamamen uyumlu 32bit/64bit 33MHz PCI desteği (bazı aygıtlarda 66MHz)

IOB Yapısı : Giriş/Çıkış Bloğu (IOB), FPGA’in dâhili lojiği ile bir kılıf pini arasında programlanabilir tekyönlü yâda çiftyönlü bir arayüz sağlamaktadır. Tekyönlü sadece-giriş bloğu tüm IOB kapasitesinin bir altkümesine sahiptir. Böylece, çıkış yolu için herhangi bir lojik yâda bağlantı bulunmamaktadır. Sadece giriş bloklarının sayısı aygıtın boyutuna göre değişmekle beraber asla toplam IOB sayısının % 25’ini aşmamaktadır.

I/O Kümelere Ayırma (Banking) : Şekil 3.4’de gösterildiği gibi Spartan-3E mimarisinde IOB’lar dört I/O kümesine bölünmüştür. Her bir küme ayrık VCCO ve VREF kaynakları ile sürülmektedir. Ayrık kaynaklar her bir kümenin bağımsız VCCO ile beslenmesine olanak sağlamaktadır. Benzer şekilde, VREF gerilimi her bir küme için ayarlanabilir.

Sayısal Saat Yöneticisi (DCMs) : Spartan-3E Sayısal saat yöneticisi (DCM) saat frekansı, faz kayması ve eğri üzerinde tamamen esnek bir kontrol sağlamaktadır. Bunu başarmak için DCM, farklı sıcaklık ve gerilim şartları altında dahi saat sinyali karakteristiğini yüksek oranda kesinlikle çalışmasını sürdürmek için geribesleme kullanan tamamen sayısal bir kontrol sistemi olan Gecikme-Kilitlemeli Çevrim (DLL) kullanmaktadır. Spartan-3E içerisindeki DCM lojik diziler içerisindeki CLB’ler tarafından çevrilmiştir. Sayısal saat yöneticisi bir tasarım içerisinde “DCM” örneği (primitive) kullanılarak oluşturulur.

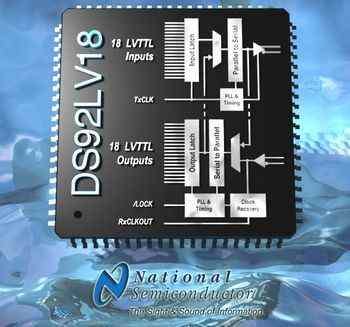

DS92LV18 18-Bit Bus LVDS Serializer/Deserializer

Genel Tanım :DS92LV18 Paralel-seri/Seri-paralel dönüştürücü (SERDES) çifti bir BLVDS içindeki 18-bit paralel veriyi gömülü saat bilgisiyle beraber seri veri dizisine çevirmektedir. Bu tek seri dizi kablo ve PCB yolları üzerindeki 18-bit (yâda daha az) verinin transferini saat yolu ve paralel veri arasındaki eğri (skew) problemlerini yok ederek basitleştirmektedir. Veri yolunun daraltılması ile PCB katman sayısı, kablo genişliği, konektör boyu ve pinlerini azaltarak sistem maliyetinden kazanım sağlamaktadır.

Bu SERDES çifti gömülü sistem ve aygıt test kabiliyetine sahiptir. Hat geri-çevrim özelliği kullanıcının alıcı çıkışında seri veriden paralel veriye çevrim yapılırken alıcı ve vericinin seri veri iletişim yolunun güvenilirliğini kontrol edebilmesini sağlar. Yerel geri-çevrim özelliği kullanıcının yerel paralel-veriyolu tarafında alıcının güvenilirliğini kontrol edebilmesini sağlar.

DS92LV18 değiştirilmiş BLVDS işaretleşmesini yüksek-hızlı I/O üzerine dâhil etmektedir. BLVDS, bir seri iletişim yolu üzerinde güvenilir veri transferi için düşük güç ve düşük gürültülü ortam sağlamaktadır. Fark veri yolu içerisinden geçen eş ve karşıt akımlar kenar alan sonuçlarını birleştirerek EMI’yi kontrol etmektedir.

Özellikleri

• 15–66 MHz 18:1/1:18 Paralel-Seri/Seri-Paralel dönüştürücü (2.376 Gbps çift yönlü iletişim hızı)

• Ayrık saat, yetkilendirme ve güç kesme pinleri ile beraber bağımsız alıcı ve verici işlemleri

• Yerel olarak oluşturulan saat sinyalini kullanan kolay sistem tasarımı için geniş ± %5 referans saat frekansı toleransı

• Hat ve Yerel geri-çevrim modları

• Düşük EMI için backplane ve kablolar içinden sağlam BLVDS seri iletişim

• Harici kodlama gerektirmez

• Dâhili PLL’e sahiptir, ayrıca harici PLL bileşenleri gerektirmez

• Tek +3.3V güç kaynağı

• Düşük güç: PRBS–15 Paternli 66MHz sinyal ile 90mA (tipik olarak) verici

• ±100 mV alıcı giriş eşiği

• Kilitlenme kaybı tespit ve raporlama pini

• Endüstriyel −40 to +85°C sıcaklık aralığı

• >2.0kV HBM ESD

• Küçük ve standart 80-pin LQFP kılıf seçenekleri

işlevsel Tanım : DS92LV18 paralel-seri ve seri-paralel dönüştürücüyü tek bir yonga üzerinde birleştirmektedir. Paralel-seri dönüştürücü 18-bitlik bir LVCMOS veya LVTTL veri yolunu alır ve bunu gömülü saat bilgisi ile beraber seri veri dizisi şekline dönüştürür. Sonra seri-paralel dönüştürücü saat ve veriyi yeniden elde ederek 18-bit genişliğindeki sonucu çıkışa verir.

Veri Transferi : Başlatma işleminden sonra, DS92LV18 Paralel-seri dönüştürücü verileri Seri-paralel dönüştürücüye aktarabilmektedir. Seri veri dizisi paralel-seri dönüştürücü tarafından eklenen on sekiz veri bitlerini belirten başla ve dur bitlerini içermektedir. Başla biti her zaman yüksek, dur biti de her zaman düşük seviyedir. Başla ve dur bitleri aynı zamanda seri dizi içerisinde gömülü saat bitleri olarak işlev görmektedir.

VHDL’E Giriş

VHDL Nedir ?

VHDL sayısal elektronik sistemleri tanımlamak ve bir FPGA içine gömmek için kullanılan bir programlama dilidir. Bu dil Birleşik Devletler Hükümeti’nin Çok Yüksek Hızlı Tümdevreler (Very High Speed Integrated Circuits-VHSIC) programı çerçevesinde 1980 yılında başlatıldı. Program çerçevesinde geliştirme çalışmaları sürerken tümdevrelerin (ICs) yapılarını ve fonksiyonlarını tanımlamak için standart bir programlama diline ihtiyaç duyulduğu anlaşıldı. Bu sebepten dolayı VHSIC Hardware Description Language (VHDL) geliştirildi.

VHDL 1986’da IEEE standardı olması için IEEE’ ye teklif sunuldu. 1987’nin Aralık’ında IEEE 1076 standardı olarak kabul edilmesine kadar VHDL birçok revizyona uğradı.

VHDL Yapısı

Birinci olarak bir tasarımın yapısı tamamen VHDL ile tanımlanabilir. Bu tasarımı alt tasarımlara ayrıştırır ve bu alt tasarımların birbirleriyle bağlantıları sağlanabilir. ikinci olarak bu dil yakın bir programlama dili olan dillerle hazırlanmış fonksiyonların kullanılmasına izin verir. Üçüncü olarak yapılan tasarımlar işlevi olan sistemde kullanılmadan önce simülasyonu yapılabilir. Tasarımcılar hızlı bir şekilde alternatifleri geliştirip bir prototip olmadan bu alternatiflerin doğruluklarını sınayabilirler.

Özgül Bir VHDL Örneği

Burada basit ve tipik bir VHDL örneği incelenecektir. Bu örnekte iki bitlik bir sayıcının VHDL ile tanımlaması verilmiştir. Bu örnek en azından bu programlama dilinin nasıl kullanılacağı hakkında bir ön fikir verme açısından önemlidir. Burada tasarım tanımlanmaya, program için dışarıyla bağlantı sağlayan ve dışsal ara yüz görevi gören portları tanımlamakla başlanıyor.

entity count2 is

generic (prop_delay : Time := 10 ns);

port (clock : in bit;

q1, q0 : out bit);

end count2;

Yukarıdaki program parçasında count2 diye bir tasarımın varlığından söz ediliyor. Bunun yapısında clock isminde bir giriş ve q1,q2 isminde iki çıkış olduğu bildiriliyor. Bunların veri tipinin de bit olduğu belirtiliyor. Ayrıca time tipinden generic, ilk değeri 10ns olan, prop_delay (yayılma zamanı) tanımlanmaktadır.

FPGA ve ASIC içerisine Gömülü LVDS I/O’lar

En yeni Alan Programlamalı Kapı Dizileri (FPGA) ve Uygulamaya Özgü Tümleşik Devreler (ASIC), Bus LVDS uygulama alanına girmektedir. Bu yeni ürün arzları tipik çoknoktalı topoloji ile daha fazla uyumlu olması için tasarlanmış gelişmiş LVDS sürücü karakteristiklerine sahiptir. Bu FPGA platformlarında farklı çözümler üzerinde avantajlar ve dezavantajlar vardır. Örnek olarak, bir PCB üzerindeki daha az yonga, genel olarak daha az arabağlantılı basit tasarımlara götürür ve bütünleşik çözümler kart boyutu bir sorun olduğunda bazen kaçınılmazdır.

Devre Şeması Tasarımı : Buraya kadar devrenin tasarımı için gerekli bilgi ve altyapı oluşturuldu. Bu noktadan sonra devre tasarımına geçilebilir. ilk aşama FPGA ile PCI veri yolu arasında bağlanacak sinyallerin ve bu sinyallere karşılık gelecek FPGA pinlerinin belirlenmesidir. Bölüm 2.2’de şekil 2.1’de görülen gerekli sinyaller ve opsiyonel INTA# sinyali ile beraber toplam 50 adet PCI sinyali, kullanacağımız sinyaller olacaktır.

Hazırlayan: Ahmet KALE teşekkürler.

pci-fpga-vhdl-serializer-deserializer-lvds-serdes ve Eagle ile çizim Hakkında detaylı Türkçe bilgi yukarıda Özet verilmiştir Anlatımın Tamamı;

Şifre-Pass: 320volt.com

Yayım tarihi: 2008/11/30 Etiketler: Deserializer, eagle, fpga, LVDS, PCI, SERDES, Serializer, tasarım, veri yolu, VHDL

Teşekkürler