Bir çok giriş hattından gelen bilgilerden birisini seçerek uygun çıkış hattına yönlendirilmesini sağlayan birleşik devrelere “çoklayıcı / veri seçici devreler” (multiplexer) denir ve ÇOĞ (MUX) sembolü ile gösterilir. Veri çoklayıcılar, orijinal isminden hareketle çoğu kere “multiplexer” olarak adlandırılmaktadır.

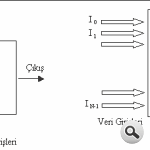

Şekil 1’de sembolü ve fonksiyon şeması görünen veri seçici devresinde girişteki bilgilerden uygun olanının seçilmesi işlemi seçme girişleri (select inputs) ile yapılır. Veri seçicilerde, 2n sayıdaki giriş hattından uygun olanı seçmek için “n” sayıda seçme hattına ihtiyaç vardır. Dijital olarak kontrol edilebilen çok pozisyonlu anahtar gibi işlem yapan veri seçiciler, seçme hattının girişlerindeki değere göre çıkışa aktarılacak giriş hattına karar verir

Şekil 1 Multiplexer sembolü ve fonksiyon şeması.

Çok sayıdaki giriş bilgisinin, zaman paylaşımlı olarak sırayla çıkışa aktarılması olayı, “multiplexing – veri seçme / çoklama” olarak tanımlanır (Şekil 1). Bir çok veri transferi, zaman paylaşım tekniği kullanılarak multiplexer devreleri yardımıyla gerçekleştirilir.

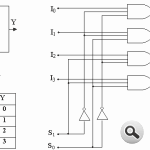

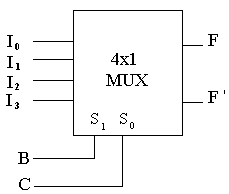

Şekil 2’deki4 girişli multiplexer devresinde; S0girişlerinin kombinasyonuna göre, girişlerden birisi çıkışa aktarılır. Her bir giriş verisi farklı seçme kombinasyonuna sahiptir.

Örneğin I0 girişi S0 = 0, S1 = 0 kombinasyonu sonucu çıkışa aktarılırken, I2 girişi S0 = 0, S1 = 1 kombinasyonu sonucu çıkışta görülür. 4×1 MUX olarak isimlendirilen bu devreye benzer şekilde, iki, sekiz ve onaltı girişli multiplexer devreleri TTL ve CMOS entegre olarak piyasada bulunmaktadır.

Şekil 2 4×1 MUX blok şeması ve fonksiyon tablosu ve lojik devresi

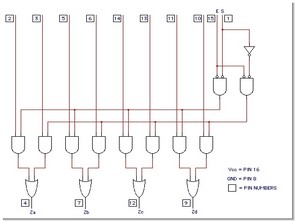

Birden fazla çoklayıcı içeren entegrelerde, elemanın çalışmasını kontrol eden bir yetkilendirme girişi (E) ile çıkışta normal ve terslenmiş çıkışların oluşmasını sağlayan kontrol girişleri bulunabilir. Şekil 3’ de görülen 8×1 MUX devresinde, E = 0 olduğu zaman S2, S1, S0 seçici girişleri veri girişlerinden birisini (I0 – I7), ‘Y’ çıkışına göndermek üzere seçer. E = 1 olduğunda ise, seçici girişlerin durumlarına bakılmaksızın Y = 0 değeri alınır.

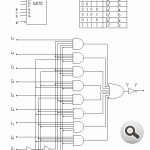

Multiplexerleri paralel bağlayarak giriş sayısını artırmak mümkündür. Şekil 4’ de 8 girişli iki multiplexer ile 16 girişli multiplexer oluşturulması görülmektedir. Bu bağlantıda iki multiplexerin çıkışı birleştirilerek tek çıkış haline getirilmiştir. S3, S2, S1, S0 seçici girişleri ile, 16 veri girişinden birisinin çıkışa aktarılması mümkündür. S3 seçici girişi multiplexerlerden hangisinin aktif olacağına karar verir. S3 = 0 olduğu zaman, üstteki multiplexer yetkilendirilir. S2, S1, S0 seçici girişleri, üstteki multiplexer girişlerinden hangisinin Q çıkışında görüleceğini belirler. S = 1 durumunda ise, alttaki girişlerden birisinin Q çıkışında görülmesini sağlar.

Şekil 3. 74151 entegresi lojik sembolü, doğruluk tablosu ve lojik devresi.

Aynı entegrenin içerisinde iki veya daha fazla sayıda çoklayıcı bulunduğunda, çoklayıcılara ait seçme ve yetkilendirme girişleri çoklayıcının tamamı için ortak kullanılabilir. Örneğin, 74151 entegresinde dört adet iki girişli multiplexer bulunur. Bu multiplexerler iki adet 4girişli multiplexer olarak kullanılabilir.

Entegrenin 4 girişli multiplexer olarak kullanılma durumunda, multiplexerin tamamındaki iki hattan birisini seçmek için bir adet ‘S’ seçme hattı yeterli olur. (şekil 3). Eı yetkilendirme multiplexerleri E = 0 olduğu zaman yetkilendirir. Multiplexerlerin yetkilendirilmesi ve S = 0 olması ile A girişlerinden birisi çıkışa bağlanır. S = 1 olduğunda ise, B girişlerinden birisi çıkışa ulaşır. Bu durumda devrenin lojik sembolü ve doğruluk tablosu şekil 5 deki gibi çizilebilir.

Şekil 4. iki adet 8 girişli multiplexer ile 16×1 multiplexer yapımı.

Daha önceki kısımlarda bahsedildiği üzere, multiplexer devrelerinin çalışma şekli kod çözücü devrelere çok benzer. Bu nedenle kod çözücü devreler multiplexer olarak kullanılabilir. Kod çözücü devrenin çıkışı, multiplexerin giriş hatlarıyla kontrol edilir.

Gerçekleştirilen fonksiyona dahil edilmeyen kombinasyonlar ilgili giriş hatları 1’e eşitlenerek seçilirken, fonksiyona dahil edilmeyen kombinasyonlar giriş hatları 0’ a eşitlenerek yetkisizlendirilir.

Şekil 5. 74157 ile yapılan 4 girişli multiplexerin sembolü, doğruluk tablosu ve lojik şeması.

Multiplexer Uygulamaları

Çeşitli dijital sistemlerde farklı uygulama alanlarında kullanılır. Örnek uygulama alanları, veri yönlendirme, işlem sıralama, paralel seri dönüşümü, lojik bir fonksiyon üretimi vb. şeklinde sıralanabilir. Bu uygulama alanlarından. Bir kısmına örnekler verelim.

Boolean Fonksiyonunun multiplexer ile gerçekleştirilmesi

‘n’ değişkenli herhangi bir fonksiyonu, 2n-1giriş / 1 çıkışlı multiplexer ile gerçekleştirmek mümkündür. Boolean fonksiyonun multiplexer ile gerçekleşmesinde, n+1 değişkenli bir fonksiyonun değişkenlerinden ‘n’ tanesi bir multiplexerin seçme hatlarına bağlanırken, kalan tek değişken multiplexer girişleri için kullanılır. Örneğin A, Aı, 1, 0 olarak seçilir. Bu dört değerin multiplexer girişlerine, diğer değişkenlerin (B,C) seçici girişlere uygulanması ile, Boolean fonksiyonun multiplexer ile gerçekleştirilmesi mümkün olur. (şekil 6).

Verilen boolean eşitliğini multiplexer yardımıyla gerçekleştirmek için, multiplexer uygulama tablolarının oluşturulması gerekir. Fonksiyonun uygulama tablolarının oluşturulması ile, multiplexerin girişlerine uygulanacak bilgiler bulunur.

Şekil 6. Boolean fonksiyonun multiplexer ile gerçekleştirilmesi

Uygulama tablosu oluşturma işleminde takip edilecek sırayı örnek bir uygulama ile birlikte açıklayalım. Açıklama sırasında, üç değişkenli bir fonksiyonda en yüksek değeri ifade eden A değişkenin giriş olarak kullanıldığını kabul edeceğiz.

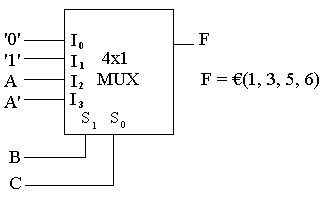

F(A,B,C)=€ (1, 3, 5, 6) fonksiyonun 4×1 multiplexer ile gerçekleştirilmesine yardım edecek uygulama tablosunu çıkaralım:

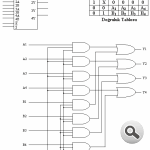

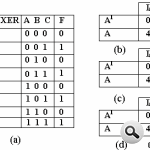

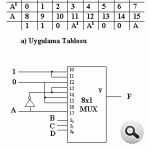

1- Boolean fonksiyonunun ifade ettiği değerler doğruluk tablosunda gösterilir. Doğruluk tablosunda kombinasyonlar sıralanarak, çıkışta ‘1’ oluşması istenen kombinasyonlar belirlenir (şekil 7a).

2- Multiplexer girişlerinin isimleri yatay olarak yazılarak, altlarına iki sıra halinde bütün mintermler sıralanır. Sıralamada, ilk satırda A=0 olan mintermler, ikinci satırda A=1 olan mintermler yer alır (şekil 7b). İlk satır Aı, ikinci satır A olarak isimlendirilir.

3- Doğruluk tablosunda çıkışın ‘1’ olduğu mintermler değerleri daire içine alınır (Şekil 7c).

Şekil 7. multiplexerlerde doğruluk ve uygulama tablolarının oluşturulması.

4- Her bir sütun ayrı ayrı incelenir. Bir sütundaki iki minterm daire içerisine alınmışsa ilgili multiplexer girişine ‘1’ iki mintermde daire içerisine alınmamışsa ilgili multiplexer girişine ‘0’ uygulanacağını gösteren işaretleme yapılır. (Şekil 7d).

5- Değişkenin kendisinin temsil edildiği alt minterm (örneğimizde A) daire içerisine ilgili multiplexer girişine A, değişkenin değilinin (Aı) temsil edildiği minterm daire içersine alınmışsa ilgili multiplexer girişine Aı uygulanacağını gösteren değerler verilir.(Şekil 7d). Böylece uygulama tablosu tamamlanır.

Elde edilen uygulama tablosu 4×1 MUX devresine uygulanırsa şekil 8’ de görülen devre oluşur. Oluşan devrede B ve C değişkenleri seçme girişlerine uygulanırken, multiplexer girişleri 0, 1 , A, Aı şeklinde değer alır.

Şekil 8. F = €(1, 3, 5, 6) fonksiyonunun 4×1 MUX ile oluşturulması

Seçici girişleri BC =00 durumunda iken, I0 girişi seçilir ve I0=0 olduğunda F=0’ dır. Dolayısıyla iki kombinasyonda, yani m0= Aı Bı Cı ve m4 = A Bı Cı değerlerinde F=0 olur. Çünkü BC=00 iken, A değeri ne olursa olsun çıkış 0’ dır.

BC=01 iken I1=1 olduğundan F=1 olur. Bunun anlamı, Aı Bı Cı ve m5= A Bı Cı kombinasyonlarında F=1 olmasıdır. Çünkü BC=01 iken, A değeri ne olursa olsun çıkış 1’dir.

BC=10 iken I2 girişi seçilir ve bu girişe A bağlı olduğu için m6=A B Cı kombinasyonunda F=1 olur. Ancak m2=Aı B Cı kombinasyonu için A=0 olacağından I2 seçili iken F=0 değerini alır.

Son olarak, BC=11 olduğunda, I3 girişi seçilir ve bu girişe Aı bağlı olduğu için m3= Aı B C kombinasyonunda F=1 olur. Ancak m7=ABC kombinasyonu için F=0 değerini alır. Bu bilgiler şekil 8’ deki doğruluk tablosunda özetlenen bilgilerin analitik açıklamasından başka bir şey değildir.

Multiplexerlerin girişlerindeki değişkenlerden en soldakini değil de, başka bir değişkeni multiplexer girişi olarak kullanmak istiyorsak, uygulama tablosunda gerekli değişikliği yapmak şartı ile istediğimiz değişkeni multiplexer girişi için seçebiliriz.

Örnek 1: F(ABC) = €(1, 3, 5, 6) fonksiyonunu 4×1 MUX ile gerçekleştireceğimizi ve S1 ve S0 seçme girişleri için A ve B değişkenlerini, multiplexer için C değişkenini kullanacağımızı varsayalım.

C değişkeni çift sayılarda tümlenip tek sayılarda tümlenmeyeceğinden, uygulama tablosundaki iki minterm satırının düzenlemesi şekil 9.a’ daki gibi oluşur.

Şekil 9. 4×1 multiplexer devre uygulaması

F= €(1,3,5,6) fonksiyonunu, oluşan tabloya yukarıdaki kuralları göz önüne alarak uygularsak, şekil 9. b’ deki uygulama tablosu oluşur. Bu tablodan çıkış bağlantılarının yapılması ile şekil 9.c’ deki multiplexer bağlantısı ortaya çıkar.

Örnek 2: F(A,B,C,D) = €(0,1,3,4,8,9,15) fonksiyonunu 8×1 multiplexer ile gerçekleştirelim.

Dört değişkenli bir fonksiyon olduğundan, üç seçme hattı ve sekiz girişli bir multiplexer’ e ihtiyaç vardır. A değişkeni veri girişine, BCD değişkenleri seçme girişlerine uygulanırsa, şekil 10’ daki uygulama tablosu oluşur. Oluşan uygulama tablosunun ilk satırının Aı ikinci satırının A olduğunu göz önünde bulundurulur ve yukarıda bahsedilen işlemler yapılırsa şekil 10.a’ daki uygulama tablosu elde edilir. Uygulama tablosundan elde edilen bilgileri; 8×1 MUX’ a uyarlanması ile şekil 10.b’ deki lojik devre çizilir.

Şekil 10. Dört değişkenli Boolean fonksiyonun multiplexer ile gerçekleşmesi

Bileşik Devrelerin Multiplexer Kullanılarak Tasarlanması

Bileşik devreler doğrudan multiplexer kullanılarak tasarlana bilir. Tasarım sırasında genel olarak lojik devre tasarımında kullanılan işlem sırası takip edilir. Tasarım aşamalarını örnek uygulama ile inceleyelim.

Örnek 3: aşağıda tasarım özellikleri verilen lojik devreyi 74151 multiplexer entegresi kullanarak gerçekleştirelim.

Tasarım özellikleri: Küçük bir şirketin 10 hissesi bulunmakta ve her hisse, hissedarlar toplantısında hisse sahibine bir oy hakkı vermektedir. 10 hissenin 4 hissedar arasındaki paylaşımı; Hissedar A=1hisse , Hissedar B=2 hisse, Hissedar C=3 hisse, Hissedar=4 hisse şeklindedir. Hissedarların her birinin önünde, hisse sayısı oranı temsil eden ve evet için kapanan, hayır için açılan bir anahtar bulunmaktadır.

Şekil 11. Multiplexer yardımıyla tasarlanması istenen bileşik devre blok şeması.

Yapılan oylamalarda, evet oyu veren toplam hisse sayısını gösteren bir devre tasarlanması istenmektedir. Bütün hissedarların karar için, evet oyu kullanması halinde ekranda ‘0’ görülmesi yeterlidir. Gerekli sayıyı göstermek için, 7 parçalı gösterge ve kod çözücü kullanılacaktır. Hissedarların anahtarlarından gelen verileri 7447 kod çözücü entegresinde kullanılacak şekilde BCD’ ye dönüştüren bileşik devreyi, dört adet 8×1 multiplexer entegresi (74151) kullanarak gerçekleştirelim (şekil 11.).

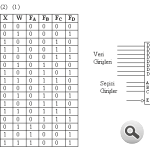

1- Her bir hissedarın temsil ettiği oy oranı farklı olduğundan, hissedarların evet dedikleri zamandaki değerleri BCD’ ye çeviren doğruluk tablosu oluşturulur (şekil 12.). Doğruluk tablosunda giriş değişkenleri olarak z, y, x, w harfleri, çıkış değişkenleri olarak FA, FB, FC, FD sembolleri kullanılacaktır.

2- Doğruluk tablosu çıkış sütunlarında oluşan bilgilerin her birisi ayrı uygulama tablosuna taşınır (şekil 13.).

3- Her biri 7447’ yi sürecek ikili bilgilerden birisini temsil eden multiplexer çıkışları elde edilir.

4- Uygulama tablosundaki verilen multiplexer bağlantısında kullanılması ile oluşturulan multiplexer çıkışları 7447 kod çevirici entegreyi sürmek için kullanılır (şekil 13.).

Şekil 12. Kod Çevirici İşleminin Doğruluk Tablosu ve 74151 Entegresi Fonksiyon Şeması

Dört adet multiplexerin çıkışlarından alınan bilgiler (FA, FB, FC, FD) 7447 entegresinin girişlerine verilirse, oylama sonucu elde edilen ve BCD koduna dönüştürülen sayı, yedi parçalı göstergede gözükür. Tüm hissedarların ‘Evet’ kullandığı durumda elde edilen onlu ‘10’ değerini göstermek için iki gösterge kullanılabilir.

Veri Yönlendirme (Data Routing)

Multiplexerler, bir çok kaynaktan gelen veriyi tek bir hedefe doğru yönlendirebilirler. 74157 Multiplexerin kullanıldığı yerlerden birisi, iki BCD sayıcının herhangi birinin içeriğini, tek bir kod / sürücü ve LED gösterge seti kullanılarak görüntülemektedir. Multiplexerin veri yönlendirme amacıyla kullanıldığı iki basamaklı iki sayıcı devresinin yapısı, şekil 14’ de görülmektedir.

Şekil 14’ deki devrede her bir sayıcı iki tane kas kat BCD kademesi içerir ve her biri kendi ‘clock’ sinyali ile sürülür. Sayıcı seçme (counter select) hattı ‘1’ olduğu zaman, 1’ nolu sayıcının çıkışları multiplexerler üzerinden geçerek kod çözücü / sürücü devrelere ulaşır ve göstergelerde gözükür. Bunun nedeni, kullanılan multiplexerin birbirinden bağımsız iki adet 4×1 MUX’ a sahip olması ve seçme girişinin değerine göre bunlardan birinin aktif hale gelmesidir Sayıcı seçme girişi ‘0’ olduğu zaman, 2 nolu sayıcı çıkışları multiplexerler üzerinden geçer ve göstergelerde belirir.

Anlatılardan , sayıcılardan birisinin onlu içeriğini sayıcı seçme girişinin kontrolü altında göstergelerde okunacağı bulunur. Oluşan işlem, ‘veri yönlendirme’ olarak isimlendirilir. Veri yönlendirme işleminin yaygın kullanılma yerlerinden birisi dijital saatlerdir.

Multiplexer dijital saatlerde kullanılmasıyla çok sayıda bilginin (saatler, günle, v.b.) aynı göstergede gözükmesi mümkün olur. Bu kullanım zaman paylaşımı şeklinde kullanışın yanı sıra, devrenin karmaşıklığı, hatların sayısı ve güç kullanımında avantaj sağlar.

Paralel bilgilerin seriye çevrilmesi (Paralel-to-Serial Conversiyon) ve yapılacak işlemlerin sıralanması (Operation Sequencing) multiplexer devrelerin diğer kullanım alanlarıdır.

Emeği geçen Kişilere Teşekkürler

Yayım tarihi: 2008/10/27 Etiketler: BCD değişkenleri, Boolean fonksiyonu, çoklayıcılar, lojik devresi, multiplexer, MUX, sayıcı, seçici devreler, veri seçiciler

şekil 13 ‘ten bahsediliyor yazıda ancak şekil 13’ yok

bi yanlışlık mı var acaba ?

“Şekil 7. multiplexerlerde doğruluk ve uygulama tablolarının oluşturulması.”

bu şekilde hata var, doğruluk tablosu yanlış oluşturulmuş daha doğrusu sadece 7. satır 1 değil 0 olacak 6. satır ise 0 değil 1 olacak, multiplexer ın ifadesi doğru gerçi ama olsun 😀 küçük bir hata.

anlatım konu hakkında büyük bir kaynaktan alınmış bende yeni fark ettim

tamamı: http://www.mediafire.com/?p2vsetctae9mvac

Ufak hatalar var ama başarı. (B.A.M.L elek./elektronik bolumu.)

Çok yararlı oldu teşekkürler.

sakarya ünivin gururu huseyin ekiz hocamızın kitabından alıntıdır 🙂

Çok işime yarada sağolun.