CPLD ile Büyük boy TFT lcd kullanımı için faydalı feyz alınabilecek örnekler… Örneklerde Xilinx XC2-XL deney kartı ve SRAM GS74108ATP bellekler kullanılmış . BMP formatında resimler görüntüleniyor. Görüntüleme için kullanılan TFT ekran ise LQ064V3DG01

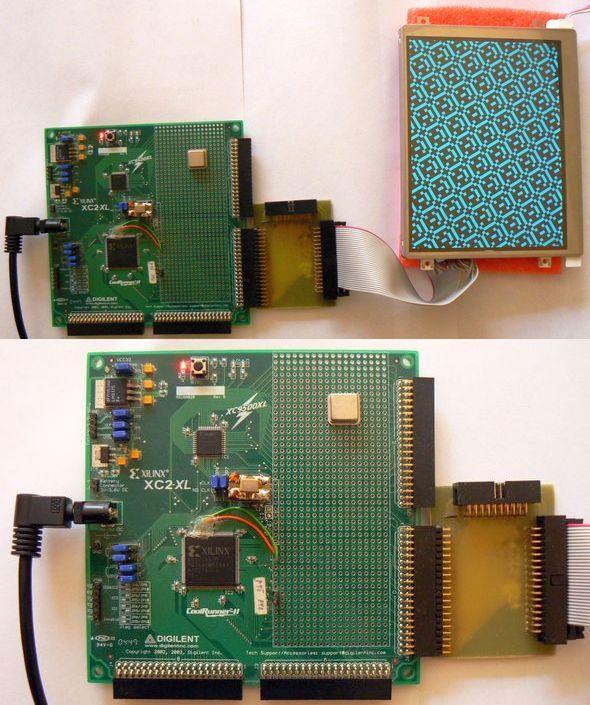

Xilinx TFT örneklerine ait kaynak kod, proje, şemalar ve SRAM pcb çizimleri var. Ek olarak yine aynı donanım ile basit bir ekran koruyucu örneğide var.

TFT’de basit modeller oluşturmaya yönelik önceki tüm girişimler, yalnızca TFT ile iletişimi doğrulamak içindi. Ancak asıl amaç, bu TFT ekran için video RAM’li eksiksiz bir denetleyici tasarlamaktı. İlk denemede paralel veri yolunu tek çipe bağlamak istemediğim için, çalışmaya oldukça uygun olan bir seri hat aracılığıyla görüntü verilerini yazarak başlamaya karar verdim.

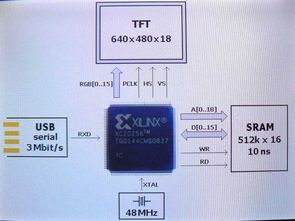

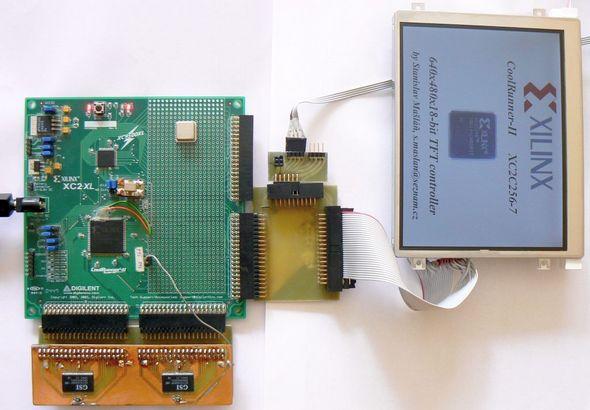

Bir CPLD olarak, XC2C256-7’yi yine Digilent’in Xilinx XC2-XL kitinde kullandım. XILINX CoolRunner2 XL kiti + 2x 512k x 16 SRAM XILINX CoolRunner2 XL kiti + 2x 512k x 16 SRAM + TFT

1. TFT ve UART için arayüz

640x480x18-bit TFT modülü, son kez olduğu gibi, yani D bağlantı noktasındaki 100R sönümleme dirençleri aracılığıyla bağlanır. Değerleri, TFT’ye giden kablonun uzunluğuna ve türüne bağlıdır, ancak neredeyse kesinlikle onlarsız çalışmayacaktır çünkü CPLD’nin kenarları çok yüksek bir dikliğe sahip.

TFT modülü statik bir ENABLE sinyali ile bağlanır, böylece modülün görünür alanı veri sayfasına göre sabit bir konumda başlar (bu sinyal kullanılarak satırların başlangıcı taşınabilir). Hafıza zaten sadece 16 bit olduğundan, ekran sadece 16 bit modunda bağlanır.

CoolRunner 2’de 5V toleranslı girişler bulunmadığından (XC9500 serisinden fark!), RXD seri girişi, uygulama notlarında önerildiği gibi bir direnç ve bir diyotla işlenir. 3V3 mantığı için gereksizdir, ancak engel teşkil etmez.

2. SRAM arayüzü

16 bit renkli 640×480 görüntü, 600 kiB bellek gerektirir, bu nedenle 512 k x 16 bit olarak kablolu bir çift 8 bit SRAM 512 kB seçtim. 10 ns’lik bir hız seçtim, çünkü daha yavaş modeller çok daha ucuz değil ve zamanlama önemli ölçüde daha zorlu olacak. Bellek, minimum özel pimlerin (yalnızca bir GSR) bulunduğu B bağlantı noktasına bağlanır. Hafızalar kısa devre ile bağlandığı için bu sefer sönümleme dirençleri olmadan yapıldı.

3. CPLD Programı

Denetleyiciyi uygulamak için temelde iki seçenek vardır. Daha ilkel varyant, birinin TFT’yi geri yüklemek için kullanıldığı ve diğerinin istendiğinde yazılabileceği/okunabileceği tamamen ayrı iki RAM belleğinin kullanıldığını varsayar. Daha sonra iki bellek, bir kontrol sinyali (çift arabelleğe alma) ile kolayca değiştirilebilir. Bu konseptin avantajı, kapı alanında basit bir yapı ve WAIT sinyali kullanmaya gerek kalmadan işlemci ile hızlı iletişimdir. Ancak dezavantajı, iki RAM’e ve özellikle çok sayıda G/Ç’ye sahip bir PLA’ya ihtiyaç duyulmasıdır ve bunlar oldukça pahalıdır.

İkinci seçenek, döngünün yarısının TFT’yi yenilemek ve diğer yarısının yeni veri yazmak için ayrıldığı zaman çoğullamada paylaşılan RAM’i kullanmaktır. Avantajı, oldukça küçük bir PLD’yi tek bir RAM ile kullanma olasılığıdır, ancak zamanlaması zor olan nispeten karmaşık bir iç yapı pahasına. Ek olarak, maksimum TFT saat ile, yani 640×480 için yaklaşık 25MB/sn, WAIT sinyali olmadan veri yazmak mümkündür.

Başlangıçta ilk varyantı kabul ettim (bu yüzden fotoğraflarda çift RAM modülü var), ancak zamanlama sorunlarını çözmeyi başardım, böylece kontrolör zorlanmadan bir çoklamada çalışıyor.

Bellek zamanlaması

Zamanlamanın gerçekte nasıl göründüğü hakkında hiçbir fikrim yok (ve bilmek bile istemem), ancak iletişim kusursuz görünüyor. Bu düzenlemedeki bellek saati yaklaşık 50 MHz’de (bant genişliğinin yarısı) çıktığı ve ilkel iki fazlı zamanlama göz önüne alındığında oldukça iyi bir sonuç olduğu için, bunun oldukça büyük bir başarı olduğunu düşünüyorum. Son sürüm için, eğer varsa, döngünün daha ince bir bölümünü, yani ideal olarak 100 MHz’lik bir ana saat kullanmak mantıklı olacaktır.

Giriş bölümünde de belirttiğim gibi, öncelikle görüntü verilerinin kaydı bir seri hat üzerinden gerçekleştirilir. Saat 3Mbit/s’ye ayarlanmıştır (FT232 için maksimum), ancak yine de 12Mbit/s’de çalışabilir. İki bayt (bir piksel) alınır alınmaz, bir döngü için bir RXC sinyali üretilir ve RAM yazma yarım döngüsü sırasında alınan piksel saklanır ve adres artırılır. Adresi butonlarla sıfırlamakla uğraşmak istemediğim için yaklaşık 500ms’lik bir zaman aşımı süresi ekledim, bundan sonra yazma adresi otomatik olarak sıfırlanıyor ve yeni bir resim yazmak mümkün oluyor.

İki yardımcı program, birlikte verilen fermuarın bir parçasıdır. Biri, 24-bit BMP’yi, denetleyicinin birlikte çalıştığı RAW 565’e dönüştürmek için kullanılır ve diğeri, dosyaları seçilen bağlantı noktasına belirli bir hızda göndermek için basit bir konsol terminalidir (daha fazlasını yapamaz).

Kaynak: elektronika.kvalitne.cz/index.html

Şifre-Pass: 320volt.com

Yayım tarihi: 2012/07/11 Etiketler: cpld, tft lcd driver, xc2xl, xilinx

Emeğinize sağlık Burhan Bey. Konuyla alakalı bir soru sorsam, Elimize geçen datasheetini bilmediğimiz lcd ekranların(siyah/beyaz, renkli) pin çıkışları nasıl bulunuyor, hangi yöntem kullanılmaktadır? Verebileceğiniz link var mı, kullanılan program, araç gereçler nelerdir? Teşekkürler Burhan Bey.