Verilog ve Xilinx ISE Kullanımı hakkında iki adet kaynak bulunuyor detaylı Türkçe bilgiler resimli program anlatımı ve örnek uygulama kodları

1- Xilinx ISE Webpack Nedir ?

Xilinx ISE Webpack Xilinx firmasının bedava dağıttığı ve Xilinx FPGAlarının üzerinde çalışılmasını sağlayan bir yazılımdır. Verilog veya VHDL ile yazılan kod sentezlenebilir ve Webpack aracılığıyla FPGA geliştirme ortamına yüklenebilir.

Xilinx ISE Webpack yazılımını indirmek için http://www.xilinx.com/ise/logic_design_prod/webpack.htm adresine gitmeniz ve kaydolmanız gerekmektedir. Kayıt olduktan sonra yazılımı indirip bilgisayarınıza kurabilirsiniz.

Yazılımı bilgisayarınıza kurduktan sonra gerekli ISE Webpack yazılım güncellemelerini yapmayı unutmayınız.

2- Xilinx ISE Webpack Kullanımı – Sentez

Yazılımın kullanımını göstermenin en iyi (ve kolay) yöntemi bir örnek olacağından bu bölümde Verilog dili ile bir kod yazıp sentezleyeceğiz. Yazdığımız kod Spartan S3E Starter Kit üzerindeki LED’leri açıp kapamaya yarayacak.

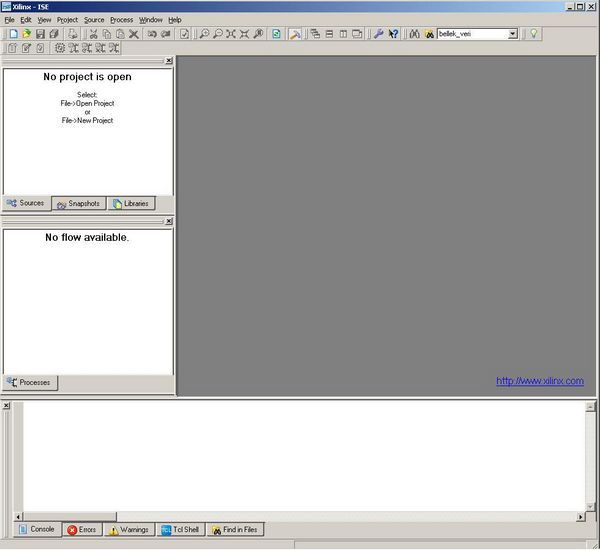

Öncelikle bilgisayarımıza kurduğumuz ISE Webpack yazılımını açalım. Aşağıdaki pencere ile karşılaşacağız:

Herhangi bir kod yazmadan önce bir proje oluşturmamız gerekmektedir. Bunu yapmak için pencerenin yukarısındaki menüden File -> New Project i seçelim. Seçtiğimiz zaman aşağıdaki pencere ile karşılaşacağız.

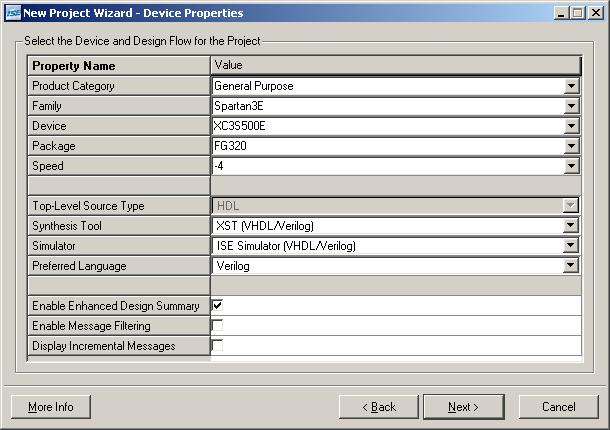

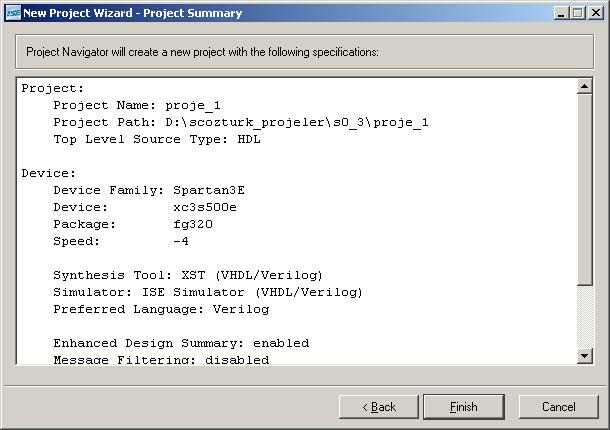

Bu pencerede Project Name kutucuğuna istediğimiz proje adını girelim. Ardından sağdaki Project Location kutucuğuna da proje dosyalarımızı konumlandıracağımız klasörü belirtelim. Top-Level Source Type için ise HDL‘i seçelim. Şimdi Next’e basabiliriz. Aşağıdaki pencere ile karşılaşacağız:

Bu pencerede kullandığımız FPGA’nın özelliklerini seçeceğiz. Product Category olarak General Purpose seçelim. Bu seçimi yapmamızın nedeni Xilinx firmasının Spartan 3E‘yi general purpose kategorisine koymasıdır. Ardından Family olarak Spartan3E‘yi seçelim. Eğer elinizde başka bir FPGA var ise uygun olan FPGA’yı listeden seçiniz. Ardından Device kutucuğuna Spartan3E‘nin hangi tipini kullandığımızı yazmamız gerekiyor.

S3E Starter Kit üzerinde bulunan S3E XC3S500E‘dir. Bu yüzden bu kutucuk için XC3S500E seçimini yapalım. Package kutucuğuna ise FG320 girelim. Eğer elinizdeki S3E Starter Kit değilse bu seçimi de farklı yapmanız gerekebilir. Speed olarak ise -4 seçimini yapalım.

Synthesis tool olarak Webpack ile beraber gelen XST (VHDL/Verilog) seçimini yapalım. Eğer elinizde farklı bir sentez programı var ise onu da kullanmanız mümkün. Simulator olarak da yine Webpack ile beraber gelen ISE Simulator (VHDL/Verilog)‘u seçelim. Preferred Language olarak ise Verilog seçelim. Diğer ayarları da yukarıdaki resimdeki gibi yaptıktan sonra Next‘e basalım. Aşağıdaki pencere ile karşılaşıyoruz:

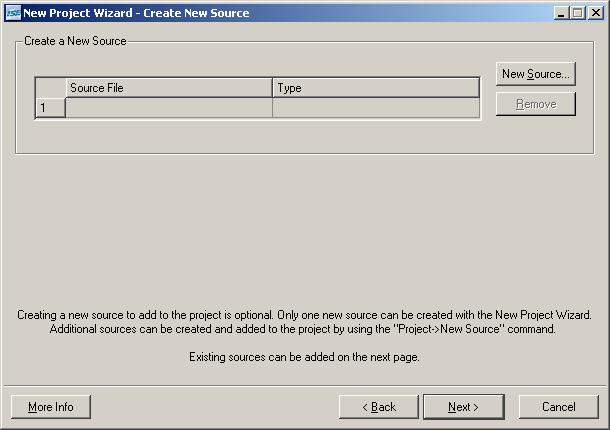

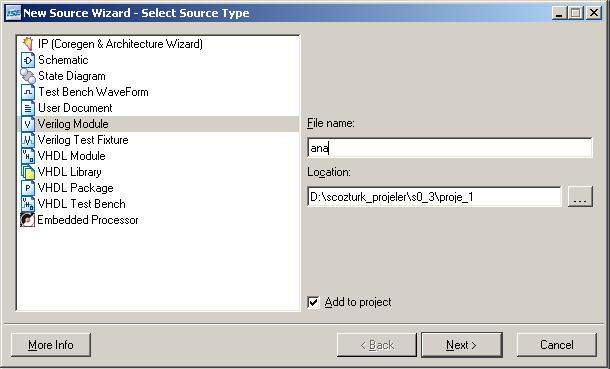

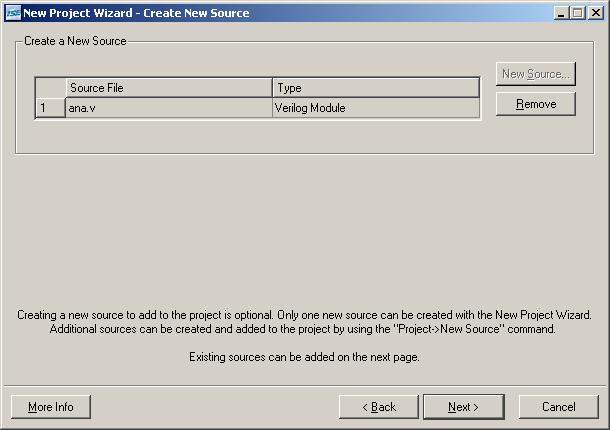

Bu pencere bizim proje dosyalarımız için bir kaynak dosya oluşturmamızı sağlıyor. Eğer bir şey değiştirmeden Next derseniz kaynak dosyalarınızı sonradan da oluşturabilirsiniz. Biz burada örnek teşkil etmesi açısından yukarıdaki New Source… düğmesine basarak kaynak dosyamızı oluşturalım. Aşağıdaki pencere ile karşılaşıyoruz:

Soldaki listeden Verilog Module‘ü seçtikten sonra File Name kutucuğuna dosyamızın adını girelim. Ardından da dosyamızın konumunu Location kutucuğuna girelim (eğer bir terslik yok ise zaten sizin için proje klasörünüzün adresi bu kutucuğa otomatik olarak yazılacaktır). Bu penceredeki Next’ etıklayalım ve bir sonraki pencereye geçelim:

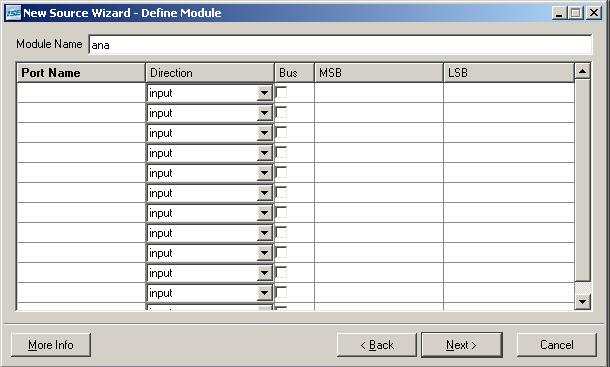

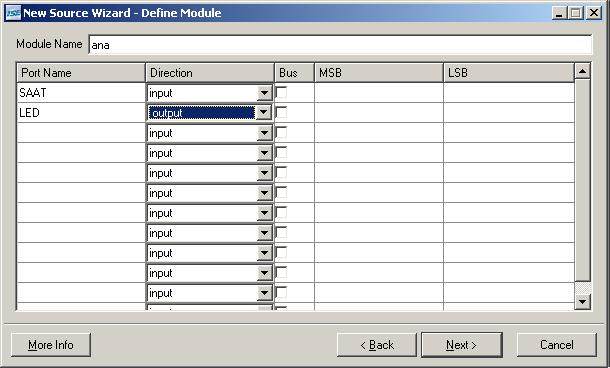

Bu pencere yardımıyla tasarımımızdaki iğneleri belirtebiliyoruz. Bu aşamada boş bırakıp geçmemizin herhangi bir sakıncası yok ama yine örnek teşkil etmesi için bu pencerede saat darbemizi ve LED çıkışımızı belirtelim. İlk olarak saat darbesi iğnesini belirtelim. Bunun için Port Name kutucuğuna SAAT yazalım. İstediğiniz başka bir adı da girebilirsizin. Direction yani iletim yönü için input yani girdi‘yi seçelim. Diğer ayarları (Bus, MSB,LSB) boş bırakabiliriz.

Ardından kullanacağımız LED’in iğnesini belirtelim. Bunun için Port Name‘e LED yazalım ve Direction olarak output yani çıktı‘yı seçelim. Yine diğer alanları boş bırakabiliriz. Yukarıdaki anlatılanları yaptığımızda penceremiz aşağıdaki hali alıyor.

Şimdi Next‘e tıklayarak diğer pencereye geçelim.

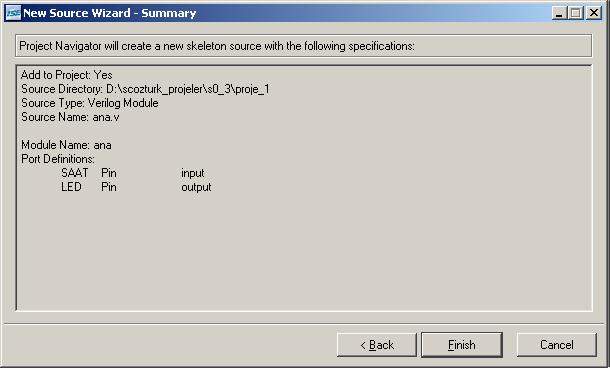

Bu pencerede az önce oluşturduğumuz kaynak dosyamız ve kapı bilgileri hakkında bilgi veriliyor. Finish‘e basabiliriz. Finish‘e bastığımızda eğer proje klasörünüz gerçekte yok ise olmadığına ama oluşturulacağına dair bir uyarı alacaksınız. Aksi takdirde herhangi bir uyarı almayacaksınız. Aşağıdaki pencere ile karşılaşıyoruz:

Oluşturmuş olduğumuz Verilog kaynağını listede görebiliyoruz. Bu örnekte daha fazla modül oluşturmak istemediğimizden Next‘e basarak bir sonraki pencereye geçelim.

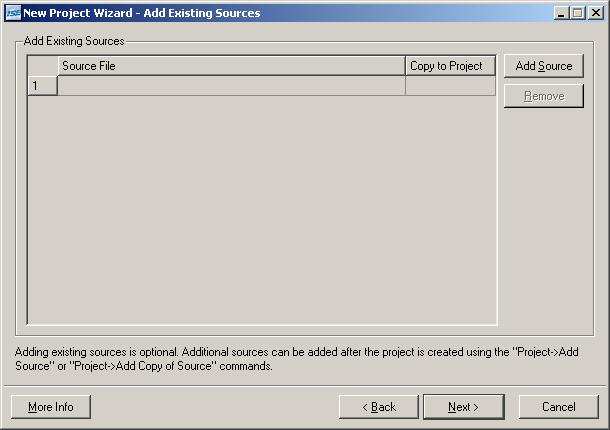

Yukarıdaki pencere ile karşılaşıyoruz. Eğer önceden oluşturduğunuz bir kaynak dosyasını oluşturmakta olduğunuz projeye eklemek isterseniz bunu buradan yapabilirsiniz. Biz bu örnekte bunu yapmayacağız ve Next’e basacağız.

Projenize yeni dosya ekleme ve var olan dosya ekleme işlemlerini sorunsuz olarak projenizi oluşturduktan sonra da yapabilirsiniz, unuttuğunuz herhangi bir şey var ise panik yapmayın sonra da ekleyebilirsiniz. Next’e tıklayalım.

![]()

Akademi.cizgi.com.tr sitesinde paylaşılan Türkçe “Verilog Tutorial” dökümanı

Verilog bir donanım tanımlama dilidir(HARDWARE DESCRIPTION LANGUAGE (HDL)). Bir donanım tanımlama dili dijital sistemleri tanımlamak için kullanılan bir dildir: örneğin, bir ağ anahtarı, bir mikroişlemci veya bir bellek veya basit bir flip-flop. Bunun anlamı, HDL kullanan biri herhangi seviyedeki herhangi bir (dijital-sayısal)donanımı tanımlayabilir.

1 // D flip-flop Code 2 module d_ff ( d, clk, q, q_bar); 3 input d ,clk; 4 output q, q_bar; 5 wire d ,clk; 6 reg q, q_bar; 7 8 always @ (posedge clk) 9 begin 10 q <= d; 11 q_bar <= ! d; 12 end 13 14 endmodule

Herhangi biri basit bir Flip flobu şekildek gösterildiği gibi tanımlayabilir, aynı şekilde 1 milyon kapısı olan karmaşık tasarımları da tanımlayabilir. Verilog, sanayide donanım tasarımı için kullanılan HDL dillerinden biridir. Bize, Davranışsal Seviyede(Behavior Level), Yazmaç Transfer Seviyesinde(Register Transfer Level (RTL)), Kapı Seviyesinde(Gate Level) ve anahtarlama seviyesinde(switch level) dijital bir tasarım yapmamıza izin verir. Verilog donanım tasarımcılarına tasarımlarını davranışsal yapıyla belirtmesine izin verir, gerçekleştirme(implementasyon) ayrıntılarını son tasarımdaki bir sonraki adıma ertelemesini sağlar.

Bu dili öğrenmek isteyen birçok mühendis, sıklıkla şu soruyu sormaktadır, Verilog öğrenmek ne kadar zaman alır? İyi haber, benim onlara cevabım, eğer daha önce bir programlama dili biliyorsanız bir haftadan fazla sürmeyeceğidir.

Tasarım Şekilleri: Verilog birçok donanım tanımlama dilindeki gibi aşağıdan yukarıya (Bottom-up) veya Yukarıdan aşağıya(Top-down) metodolojiye izin vermektedir.

Aşağıdan Yukarıya Tasarım (Bottom-Up Design): Elektornik tasarımdaki geleneksel metod ağaşıdan yukarıyadır. Herbir tasarım standart kapılar kullanılarak kapı-seviyesinde(gate-level) gerçekleşmektedir. Yeni tasarımlardaki karmaşıklık arttıkça bu metodun uygunlanmasını neredeyse imkansız kılmıştır. Yeni sistemler ASIC veya binlerce transistör içeren mikroişlemcilerden oluşmaktadır. Bu geleneksel aşağıdan yukarıya tasarım yerini yeni yapısal hiyerarşik tasarım metodlara bırakmak zorundadır. Bu yeni uygulamalar olmadan yeni karmaşıklıktaki tasarımların üstesinden gelmek imkansız olacaktır.

Yukarıdan Aşağıya Tasarım (Top-Down Design): Her tasarımcının istediği tasarım şekli yukarıdan aşağıya olanıdır. Gerçk bir yukarıdan-aşağıya tasarım erken teste, farklı teknolojilerin kolay değişimine, yapısal sistem tasarımlarına ve birçok diğer öneri avantajlarına izin verir. Ancak tam bir yukarıdan aşağıya tasarımı takip etmek çok zordur. Bu nedenlerden dolayı, birçok tasarım her iki metodun karışımı şeklinde, herbir tasarım stilinin önemli elemanları gerçeklenerek tasarlanmaktadır.

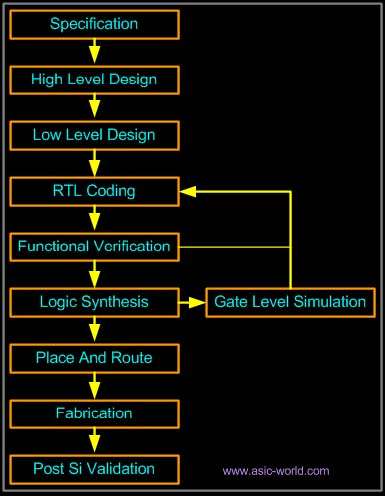

Aşağıdaki şekil Yukarıdan-Aşağıya tasarım uygulamasını göstermektedir.

Verilog Soyutlama Seviyeleri (Abstraction Levels)

Verilog birçok farklı seviyedeki soyutlamayı desteklemektedir. Bunlardan üçü çok önemlidir:

• Davranışsal seviye (Behavioral level)

• Yazmaç Transfer Seviyesi(Register-Transfer Level-RTL)

• Kapı Seviyesi (Gate Level )

Davranışsal seviye(Behavioral level): Bu seviye, koşutzamanlı (aynı zamanda olan) algoritmalar (Davranışsal) ile bir sistemi tanımlar. Herbir algoritmanın kendisi sıralıdır, bunun anlamı birbiri ardına gerçeklenen komutlar kümesini içermektedir. Fonksiyonlar (Function), Görevler (Task), ve Herzaman(Always) blokları temel elemanlarıdır. Tasarımın yapısal gerçeklemesiyle alakalı değildir.

Yazmaç Transfer Seviyesi (Register-Transfer Level): Yazmaç Transfer Seviyesi kullanarak tasarlama, bir devrenin işlemlerini ve yazmaçlar arasındaki verilerin transferinin karakteristiğini belirtir. Harici bir saat kullanılır. RTL tasarım kesin zaman kısıtları içerir: işlemler kesin bir zamanda gerçekleştirilecek şekilde planlanmıştır. Modern RTL kodun tanımı,”Sentezlenebilen herhangi bir koda RTL kodu denir”.

Kapı Seviyesi (Gate Level ): Lojik seviyesi içerisinde bir sistemin karakteristiği mantıksal bağlantılarla ve onların zamanlama özellikleriyle tanımlanmıştır. Tüm sinyaller ayrık sinyallerdir. Sadece belirli mantıksal(lojik) değerlere (`0', `1', `X', `Z`) sahip olabilirler. Kullanılabilir işlemler ilkel lojikle (AND, OR, NOT vb kapılar) önceden tanımlanmıştır. Kapı seviyesi modelleme kullanma, lojik tasarımın herhangi bir seviyesinde iyi bir fikir değildir. Kapı seviyesi kod, sentez araçlarına benzer araçlarla üretilirler ve netlist kapı seviyesi simülasyon ve arka uç için kullanılmaktadır.

Bir Günde Verilog

Her bir yeni kullanıcı Verilog’u bir günde öğrenmeyi düşler,bunun kullanmak için yeterli olmasını ister. Benim ilerde belirteceğim birkaç sayfa sizin bu hayalinizi gerçekleştirecek. Burada bazı teori ve egzersizleri takip eden örnekler olacaktır. Bu eğitsel çalışma size nasıl programlama yapılacağını öğretmez; bazı programlama deneyimleriyle tasarlanmıştır.

Bununla birlikte Verilog farklı kod bloklarını koşutzamanlı olarak gerçekler bir çok programlama dilindeki sıralı gerçeklemesinin tersine, hâla bazı paralellikler vardır. Bazı dijital tasarımdaki deneyimleri elbette faydalıdır.

Verilogdan önceki yaşam şematikle dolu bir yaşamdı. Herbir tasarım, karmaşıklığına bakılmadan , şematik üzerinden tasarlanırdı. Bunlarını doğrulanması ve hata eğilimi, uzun sürede sonuç vermekteydi, sıkıcı geliştirme süreci, doğrulama … tasarım,doğrulama… tasarım,doğrulama… şeklinde sürüp gitmekteydi.

Verilog ortaya çıktığında, lojik devreler hakkında farklı düşünce yollarına sahip olmaya başladık. Verilog tasarım döngüsü geleneksel programlama dillerindeki gibiydi, tıpkı burada bahsedeceğimiz gibi:

• Belirtimler (Specifications (specs))

• Yüksek seviyeli tasarım (High level design)

• Düşük seviyeli tasarım(Low level (micro) design)

• RTL kodlama

• Doğrulama (Verification)

• Sentez (Synthesis).

Listedeki ilk şey belirtimler(specifications)- tasarımımızdaki kısıtlamalar gereklilikler nelerdir? Ne inşa etmeye çalışıyoruz? Bu eğitsel için, iki etken arabulucusu(two agent arbiter) inşa edeceğiz: birbirine baskın çıkmaya çalışan iki etkeni seçen aygıt. Aşağıda bazı belirtimler bulunmaktadır.

• İki etken arabulucusu (Two agent arbiter).

• Aktif yüksek asenkron sıfırlama(Active high asynchronous reset).

• Sabit öncelik, 0 ‘ın 1 üzerindeki önceliği

• Onaylama istek kabul edildiği zaman kabul edilir.

Eğer belirtimlerimiz varsa, blok diyagramı çizebiliriz, bu da temelde sistemdeki veri akışının soyutlamasıdır(bloğa ne gelecek ne gidecek). Aşağıdaki örnekte bunun basit şeklidir. Henüz büyülü kara kutunun içinde ne olduğu konusunda endişe duymamaktayız.

Düşük seviyeli tasarım

Modüller, Veri Tipleri

Arabulucu("arbiter") modül kodu

Çift Yönlü(Bi-Directional) Port Örneği

Sinyal Vektörleri Örneği

Operatörler (Operator)

Kontrol İfadeleri if, else, repeat, while,for, case

Değişken Ataması

Başlangıç Bloğu(Initial Block)

Herzaman(Always) Bloğu

Atama(assign) İfadesi

Görev (Task) ve Fonksiyon (Function)

Test Benç(Test Benche)

Verilog’un Tarihçesi

Kaynak 1: yukarıda Özetler verildi anlatımın tamamı link: Xilinx ISE nedir? Nasıl kullanılır?

Şifre-Pass: 320volt.com

Yayım tarihi: 2008/03/09 Etiketler: fpga, fpga programlama, verilog, verilog nedir, verilog tutorial, xilinx, xilinx ise kullanımı, xilinx programlama

Merhaba,

verılog dersınden yapmam gereken bir projem var. projenın adı “pwm adn one bıt dac” ama nasıl yapacagım konusunda pek net fıkrım yok. ınternetten arastırdım dac ve pwm hakkında bılgı ancak ıkısnın baglantısını verılog da nasıl kuracagım onu anlayamadım. bana yardımcı olabılır yol gosterebılırsenız çok sevınırm.

ıyı calısmalar

emeğinize saglik

Linkler ölmüş